# SCANSTA112 7-Port Multidrop IEEE 1149.1 (JTAG) Multiplexer

Check for Samples: SCANSTA112

### **FEATURES**

- True IEEE 1149.1 Hierarchical and Multidrop Addressable Capability

- The 8 Address Inputs Support up to 249

Unique Slot Addresses, an Interrogation

Address, Broadcast Address, and 4 Multi-Cast

Group Addresses (Address 000000 is

Reserved)

- 7 IEEE 1149.1-Compatible Configurable Local Scan Ports

- Bi-directional Backplane and LSP<sub>0</sub> Ports are Interchangeable Slave Ports

- Capable of Ignoring TRST of the Backplane Port when it Becomes the Slave.

- Stitcher Mode Bypasses Level 1 and 2 Protocols

- Mode Register<sub>0</sub> Allows Local TAPs to be Bypassed, Selected for Insertion into the Scan Chain Individually, or Serially in Groups of Two or Three

- Transparent Mode can be Enabled with a Single Instruction to Conveniently Buffer the Backplane IEEE 1149.1 Pins to Those on a Single Local Scan Port

- General Purpose Local Port Pass Through Bits are Useful for Delivering Write Pulses for Flash Programming or Monitoring Device Status.

- Known Power-Up State

- TRST on all Local Scan Ports

- 32-bit TCK Counter

- 16-bit LFSR Signature Compactor

- Local TAPs can Become TRI-STATE via the OE Input to Allow an Alternate Test Master to Take Control of the Local TAPs (LSP<sub>0-3</sub> have a TRI-STATE Notification Output)

- 3.0-3.6V V<sub>CC</sub> Supply Operation

- Supports Live Insertion/Withdrawal

### DESCRIPTION

The SCANSTA112 extends the IEEE Std. 1149.1 test bus into a multidrop test bus environment. The advantage of a multidrop approach over a single serial scan chain is improved test throughput and the ability to remove a board from the system and retain test access to the remaining modules. Each SCANSTA112 supports up to 7 local IEEE1149.1 scan chains which can be accessed individually or combined serially.

Addressing is accomplished by loading the instruction register with a value matching that of the Slot inputs. Backplane and inter-board testing can easily be accomplished by parking the local TAP Controllers in one of the stable TAP Controller states via a Park instruction. The 32-bit TCK counter enables built in self test operations to be performed on one port while other scan chains are simultaneously tested.

The STA112 has a unique feature in that the backplane port and the LSP0 port are bidirectional. They can be configured to alternatively act as the master or slave port so an alternate test master can take control of the entire scan chain network from the LSP0 port while the backplane port becomes a slave.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

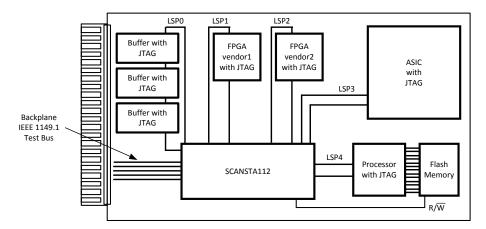

Figure 1. Typical use of SCANSTA112 for board-level management of multiple scan chains.

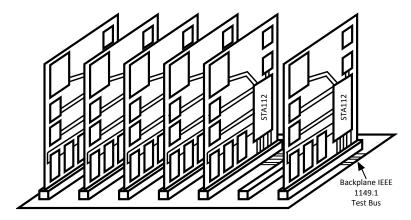

Figure 2. Example of SCANSTA112 in a multidrop addressable backplane.

### Introduction

The SCANSTA112 is the third device in a series that enable multi-drop address and multiplexing of IEEE-1149.1 scan chains. The SCANSTA112 is a superset of its predecessors - the SCANPSC110 and the SCANSTA111. The STA112 has all features and functionality of these two previous devices.

The STA112 is essentially a support device for the IEEE 1149.1 standard. It is primarily used to partition scan chains into managable sizes, or to isolate specific devices onto a seperate chain (Figure 1). The benefits of multiple scan chains are improved fault isolation, faster test times, faster programling times, and smaller vector sets.

In addition to scan chain partitioning, the device is also addressable for use in a multidrop backplane environment (Figure 2). In this configuration, multiple IEEE-1149.1 accessible cards with an STA112 on board can utilize the same backplane test bus for system-level IEEE-1149.1 access. This approach facilitates a system-wide commitment to structural test and programming throughout the entire system life sycle.

#### **Architecture**

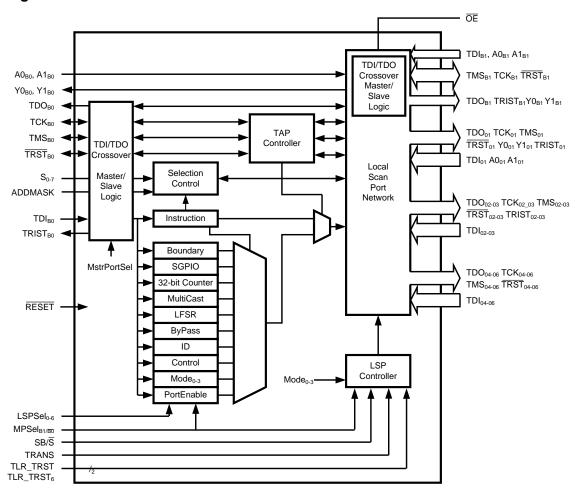

Figure 3 shows the basic architecture of the 'STA112. The device's major functional blocks are illustrated here.

The TAP Controller, a 16-state state machine, is the central control for the device. The instruction register and various test data registers can be scanned to exercise the various functions of the 'STA112 (these registers behave as defined in IEEE Std. 1149.1).

The 'STA112 selection controller provides the functionality that allows the 1149.1 protocol to be used in a multidrop environment. It primarily compares the address input to the slot identification and enables the 'STA112 for subsequent scan operations.

The Local Scan Port Network (LSPN) contains multiplexing logic used to select different port configurations. The LSPN control block contains the Local Scan Port Controllers (LSPC) for each Local Scan Port (LSP $_0$ , LSP $_1$  ... LSP $_n$ ). This control block receives input from the 'STA112 instruction register, mode registers, and the TAP controller. Each local port contains all four boundary scan signals needed to interface with the local TAPs plus the optional Test Reset signal (TRST).

The TDI/TDO Crossover Master/Slave logic is used to define the bidirectional B0 and B1 ports in a Master/Slave configuration.

## **Block Diagram**

Figure 3. SCANSTA112 Block Diagram

Copyright © 2002–2013, Texas Instruments Incorporated

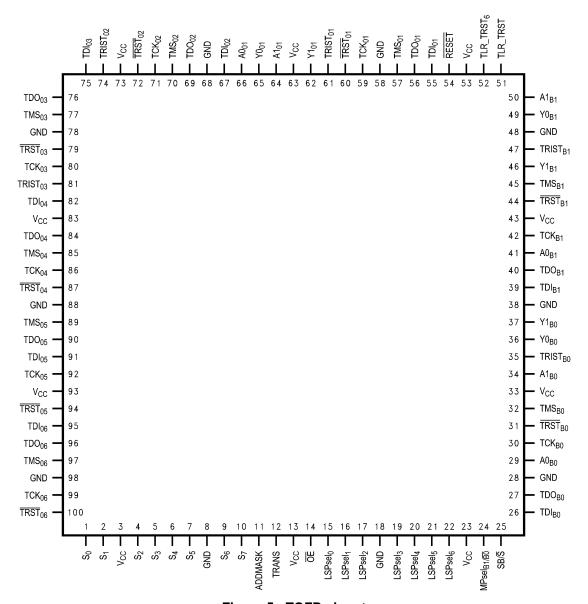

## **Connection Diagrams**

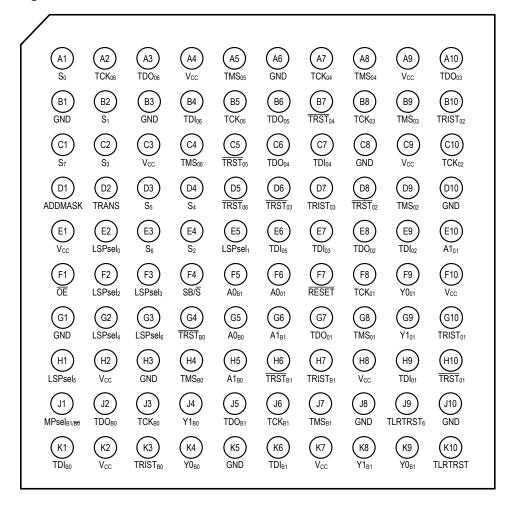

Figure 4. (NFBGA Top view)

Figure 5. TQFP pinout

### **PIN DESCRIPTIONS**

| PIN DESCRIPTIONS                                                             |             |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------------------------------------|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                     | No.<br>Pins | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| vcc                                                                          | 10          | N/A | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| GND                                                                          | 10          | N/A | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| RESET                                                                        | 1           | I   | RESET Input: will force a reset of the device regardless of the current state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| ADDMASK                                                                      | 1           | - 1 | ADDRESS MASK input: Allows masking of lower slot input pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| MPsel <sub>B1/B0</sub>                                                       | 1           | I   | MASTER PORT SELECTION: Controls selection of $LSP_{B0}$ or $LSP_{B1}$ as the backplane port. The unselected port becomes $LSP_{00}$ . A value of "0" will select $LSP_{B0}$ as the master port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SB/S                                                                         | 1           | I   | Selects ScanBridge or Stitcher Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| LSPsel (0-6)                                                                 | 7           | - 1 | In Stitcher Mode these inputs define which LSP's are to be included in the scan chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| TRANS                                                                        | 1           | I   | Transparent Mode enable input: The value of this pin is loaded into the TRANSENABLE bit of the control register at power-up. This value is used to control the presence of registers and pad-bits in the scan chain while in the stitcher mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| TLR_TRST                                                                     | 1           | I   | Sets the driven value of $\overline{TRST}_{0-5}$ when LSP TAPs are in $\overline{TLR}$ and the device is not being reset. During $\overline{RESET}$ = "0" or $\overline{TRST}_B$ = "0" (IgnoreReset = "0") $\overline{TRST}_n$ = "0". This pin is to be tied low to match the function of the SCANSTA111                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| TLR_TRST <sub>6</sub>                                                        | 1           | I   | This pin affects TRST of LSP <sub>6</sub> only. This pin is to be tied low to match the function of the SCANSTA111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| TDI <sub>B0</sub> , TDI <sub>B1</sub>                                        | 2           | I   | BACKPLANE TEST DATA INPUT: All backplane scan data is supplied to the 'STA112 through this input pin. MPsel $_{B1/B0}$ determines which port is the master backplane port and which is LSP $_{00}$ . This input has a 25K $\Omega$ internal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method). When the device is power-off (V $_{DD}$ floating), this input appears to be a capacitive load to ground (1). When V $_{DD} = 0$ V (i.e.; not floating but tied to V $_{SS}$ ) this input appears to be a capacitive load with the pull-up to ground.                                                                                                                                                                 |  |  |  |

| TMS <sub>B0</sub> , TMS <sub>B1</sub>                                        | 2           | 1/0 | BACKPLANE TEST MODE SELECT: Controls sequencing through the TAP Controller of the 'STA112. Also controls sequencing of the TAPs which are on the local scan chains. MPsel <sub>B1/B0</sub> determines which port is the master backplane port and which is LSP <sub>00</sub> . This bidirectional TRI-STATE pin has 24mA of drive current, with a 25K $\Omega$ internal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method). When the device is power-off (V <sub>DD</sub> floating), this input appears to be a capacitive load to ground <sup>(1)</sup> . When V <sub>DD</sub> = 0V (i.e.; not floating but tied to V <sub>SS</sub> ) this input appears to be a capacitive load with the pull-up to ground.        |  |  |  |

| TDO <sub>B0</sub> , TDO <sub>B1</sub>                                        | 2           | I/O | BACKPLANE TEST DATA OUTPUT: This output drives test data from the 'STA112 and the local TAPs, back toward the scan master controller. This bidirectional TRI-STATE pin has 12mA of drive current. MPsel <sub>B1/<math>\overline{\text{BO}}</math></sub> determines which port is the master backplane port and which is LSP <sub>00</sub> . Output is sampled during interrogation addressing. When the device is power-off (V <sub>DD</sub> = 0V or floating), this output appears to be a capacitive load <sup>(1)</sup> .                                                                                                                                                                                                                           |  |  |  |

| TCK <sub>B0</sub> , TCK <sub>B1</sub>                                        | 2           | I/O | TEST CLOCK INPUT FROM THE BACKPLANE: This is the master clock signal that controls all scan operations of the 'STA112 and of the local scan ports. MPsel <sub>B1/<math>\overline{\mathbb{B}0}</math></sub> determines which port is the master backplane port and which is LSP <sub>00</sub> . These bidirectional TRI-STATE pins have 24mA of drive current with hysterisis. This input has no pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method). When the device is power-off (V <sub>DD</sub> floating), this input appears to be a capacitive load to ground <sup>(1)</sup> . When V <sub>DD</sub> = 0V (i.e.; not floating but tied to V <sub>SS</sub> ) this input appears to be a capacitive load to ground. |  |  |  |

| TRST <sub>B0</sub> , TRST <sub>B1</sub>                                      | 2           | I/O | TEST RESET: An asynchronous reset signal (active low) which initializes the 'STA112 logic. MPsel <sub>B1/B0</sub> determines which port is the master backplane port and which is LSP <sub>00</sub> . This bidirectional TRI-STATE pin has 24mA of drive current, with a 25KΩ internal pull-up resistor and no ESD clamp diode (ESD is controlled with an alternate method). When the device is power-off (V <sub>DD</sub> floating), this pin appears to be a capacitive load to ground <sup>(1)</sup> . When V <sub>DD</sub> = 0V (i.e.; not floating but tied to V <sub>SS</sub> ) this input appears to be a capacitive load with the pull-up to ground.                                                                                           |  |  |  |

| TRIST <sub>B0</sub> , TRIST <sub>B1</sub> , TRIST <sub>(01-03)</sub>         | 5           | 0   | TRI-STATE NOTIFICATION OUTPUT: This signal is asserted high when the associated TDO is TRI-STATEd. Associated means $TRIST_{B0}$ is for $TDO_{B0}$ , $TRIST_{01}$ is for $TDO_{01}$ , etc. This output has 12mA of drive current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| A0 <sub>B0</sub> , A1 <sub>B0</sub> , A0 <sub>B1</sub> ,<br>A1 <sub>B1</sub> | 4           | I   | BACKPLANE PASS-THROUGH INPUT: A general purpose input which is driven to the $Y_n$ of a single selected LSP. (Not available when multiple LSPs are selected). This input has a $25 \mathrm{K}\Omega$ internal pull-up resistor. MPsel <sub>B1/B0</sub> determines which port is the master backplane port and which is LSP <sub>00</sub> .                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Y0 <sub>B0</sub> , Y1 <sub>B0</sub> , Y0 <sub>B1</sub> ,<br>Y1 <sub>B1</sub> | 4           | 0   | BACKPLANE PASS-THROUGH OUTPUT: A general purpose output which is driven from the $A_n$ of a single selected LSP. (Not available when multiple LSPs are selected). This TRI-STATE output has 12mA of drive current. MPsel <sub>B1/<math>\overline{B0}</math></sub> determines which port is the master backplane port and which is LSP <sub>00</sub> .                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

(1) Refer to the IBIS model on our website for I/O characteristics.

# **PIN DESCRIPTIONS (continued)**

| Pin Name                            | No.<br>Pins | 1/0 | Description                                                                                                                                                                                                                                                                         |

|-------------------------------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S <sub>(0-7)</sub>                  | 8           | I   | SLOT IDENTIFICATION: The configuration of these pins is used to identify (assign a unique address to) each 'STA112 on the system backplane                                                                                                                                          |

| ŌĒ                                  | 1           | I   | OUTPUT ENABLE for the Local Scan Ports, active low. When high, this active-low control signal TRI-STATEs all local scan ports on the 'STA112, to enable an alternate resource to access one or more of the local scan chains.                                                       |

| TDO <sub>(01-06)</sub>              | 6           | 0   | TEST DATA OUTPUTS: Individual output for each of the local scan ports . These TRI-STATE outputs have 12mA of drive current.                                                                                                                                                         |

| TDI <sub>(01-06)</sub>              | 6           | I   | TEST DATA INPUTS: Individual scan data input for each of the local scan ports. This input has a $25K\Omega$ internal pull-up resistor.                                                                                                                                              |

| TMS <sub>(01-06)</sub>              | 6           | 0   | TEST MODE SELECT OUTPUTS: Individual output for each of the local scan ports. TMS <sub>n</sub> does not provide a pull-up resistor (which is assumed to be present on a connected TMS input, per the IEEE 1149.1 requirement) . These TRI-STATE outputs have 24mA of drive current. |

| TCK <sub>(01-06)</sub>              | 6           | 0   | LOCAL TEST CLOCK OUTPUTS: Individual output for each of the local scan ports. These are buffered versions of TCK <sub>B</sub> . These TRI-STATE outputs have 24mA of drive current.                                                                                                 |

| TRST <sub>(01-06)</sub>             | 6           | 0   | LOCAL TEST RESETS: A gated version of $\overline{\text{TRST}}_{\text{B}}$ . These TRI-STATE outputs have 24mA of drive current.                                                                                                                                                     |

| A0 <sub>01</sub> , A1 <sub>01</sub> | 2           | I   | LOCAL PASS-THROUGH INPUTS: General purpose inputs which can be driven to the backplane pin $Y_B$ . (Only on LSP $_0$ and LSP $_1$ . Only available when a single LSP is selected) . These inputs have a $25 \mathrm{K}\Omega$ internal pull-up resistor.                            |

| Y0 <sub>01</sub> , Y1 <sub>01</sub> | 2           | 0   | LOCAL PASS-THROUGH OUTPUT: General purpose outputs which can be driven from the backplane pin $A_B$ . (Only on LSP $_0$ and LSP $_1$ . Only available when a single LSP is selected) . These TRI-STATE outputs have 12mA of drive current.                                          |

Product Folder Links: SCANSTA112

#### APPLICATION OVERVIEW

#### ADDRESSING SCHEME

The SCANSTA112 architecture extends the functionality of the IEEE 1149.1 Standard by supplementing that protocol with an addressing scheme which allows a test controller to communicate with specific 'STA112s within a network of 'STA112s. That network can include both multi-drop and hierarchical connectivity. In effect, the 'STA112 architecture allows a test controller to dynamically select specific portions of such a network for participation in scan operations. This allows a complex system to be partitioned into smaller blocks for testing purposes. The 'STA112 provides two levels of test-network partitioning capability. First, a test controller can select individual 'STA112s, specific sets of 'STA112s (multi-cast groups), or all 'STA112s (broadcast). This 'STA112-selection process is supported by a Level-1 communication protocol. Second, within each selected 'STA112, a test controller can select one or more of the chip's seven local scan-ports. That is, individual local ports can be selected for inclusion in the (single) scan-chain which a 'STA112 presents to the test controller. This mechanism allows a controller to select specific scan-chains within the overall scan network. The port-selection process is supported by a Level-2 protocol.

## HIERARCHICAL SUPPORT

Multiple SCANSTA112's can be used to assemble a hierarchical boundary-scan tree. In such a configuration, the system tester can configure the local ports of a set of 'STA112s so as to connect a specific set of local scanchains to the active scan chain. Using this capability, the tester can selectively communicate with specific portions of a target system. The tester's scan port is connected to the backplane scan port of a root layer of 'STA112s, each of which can be selected using multi-drop addressing. A second tier of 'STA112s can be connected to this root layer, by connecting a local port (LSP) of a root-layer 'STA112 to the backplane port of a second-tier 'STA112. This process can be continued to construct a multi-level scan hierarchy. 'STA112 local ports which are not cascaded into higher-level 'STA112s can be thought of as the terminal leaves of a scan tree. The test master can select one or more target leaves by selecting and configuring the local ports of an appropriate set of 'STA112s in the test tree.

### STANDARD SCANBRIDGE MODE

ScanBridge mode refers to functionality and protocol that has been used since the introduction of the PSC110 in 1993. This functionality consists of a multidrop addressable IEEE1149.1 switch. This enables one (or more) device to be selected from many that are connected to a parallel IEEE1149.1 bus or backplane. The second function that ScanBridge mode accomplishes is to act as a mux for multiple IEEE1149.1 local scan chains. The Local Scan Ports (LSP) of the device creates a connection between one or more of the local scan chains to the backplane bus.

To accomplish this functionality the ScanBridge has two levels of protocol and an operational mode. Level 1 protocol refers to the required actions to address/select the desired ScanBridge. Level 2 protocol is required to configuring the mux'ing function and enable the connection (UNPARK) between the local scan chain and the backplane bus via an LSP. Upon completion of level 1 and 2 protocols the ScanBridge is prepared for its operational mode. This is where scan vectors are moved from the backplane bus to the desired local scan chain(s).

### STITCHER MODE

Stitcher Mode is a method of skipping level 1 and 2 protocol of the ScanBridge mode of operation. This is accomplished via external pins. When in stitcher mode the SCANSTA112 will go directly to the operational mode.

### TRANSPARENT MODE

Transparent mode refers to a condition of operation in which there are no pad-bits or SCANSTA112 registers in the scan chain. The Transparent mode of operation is available in both ScanBridge and Stitcher modes. Only the activation method differs. Once transparent mode has been activated there is no difference in operation. Transparent mode allows for the use of vectors that have been generated for a chain where these bits were not included.

Check with your ATPG tool vendor to ensure support of these features.

For details regarding the internal operation of the SCANSTA112 device, refer to applications note AN-1259(SNLA055) SCANSTA112 Designers Reference.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS(1)

| Supply Voltage (V <sub>CC</sub> )                                 |            | -0.3V to +4.0V  |  |

|-------------------------------------------------------------------|------------|-----------------|--|

| DC Input Diode Current ( $I_{IK}$ ) $V_I = -0.5V$                 |            | −20 mA          |  |

| DC Input Voltage (V <sub>I</sub> )                                |            | −0.5V to +3.9V  |  |

| DC Output Diode Current (I <sub>OK</sub> ) V <sub>O</sub> = −0.5V |            | −20 mA          |  |

| DC Output Voltage (V <sub>O</sub> )                               |            | -0.3V to +3.9V  |  |

| DC Output Source/Sink Current (I <sub>O</sub> )                   |            | ±50 mA          |  |

| DC V <sub>CC</sub> or Ground Current per Output Pin               |            | ±50 mA          |  |

| DC Latchup Source or Sink Current                                 |            | ±300 mA         |  |

| Junction Temperature (Plastic)                                    |            | +150°C          |  |

| Storage Temperature                                               |            | −65°C to +150°C |  |

| Lead Temperature (Solder, 4sec)                                   | 100L NFBGA | 220°C           |  |

|                                                                   | 100L TQFP  | 220°C           |  |

| Max Package Power Capacity @ 25°C                                 | 100L NFBGA | 3.57W           |  |

|                                                                   | 100L TQFP  | 2.11W           |  |

| Thermal Resistance (θ <sub>JA</sub> )                             | 100L NFBGA | 35°C/W          |  |

|                                                                   | 100L TQFP  | 59.1°C/W        |  |

| Package Derating above +25°C                                      | 100L NFBGA | 28.57mW/°C      |  |

|                                                                   | 100L TQFP  | 16.92mW/°C      |  |

| ESD Last Passing Voltage (HBM Min)                                |            | 2500V           |  |

<sup>(1)</sup> Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. TI does not recommend operation of SCAN STA products outside of recommended operation conditions.

## RECOMMENDED OPERATING CONDITIONS

| Supply Voltage (V <sub>CC</sub> ) 'STA112          | 3.0V to 3.6V          |

|----------------------------------------------------|-----------------------|

| Input Voltage (V <sub>I</sub> )                    | 0V to V <sub>CC</sub> |

| Output Voltage (V <sub>O</sub> )                   | 0V to V <sub>CC</sub> |

| Operating Temperature (T <sub>A</sub> ) Industrial | −40°C to +85°C        |

### DC ELECTRICAL CHARACTERISTICS

Over recommended operating supply voltage and temperature ranges unless otherwise specified

| Symbol          | Parameter                                                                                                                                                                                                                                               | Conditions                                                     | Min                    | Max | Units |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|-----|-------|

| V <sub>IH</sub> | Minimum High Input Voltage                                                                                                                                                                                                                              | $V_{OUT} = 0.1V$ or                                            | 2.1                    |     | V     |

|                 |                                                                                                                                                                                                                                                         | V <sub>CC</sub> -0.1V                                          |                        |     |       |

| V <sub>IL</sub> | Maximum Low Input Voltage                                                                                                                                                                                                                               | $V_{OUT} = 0.1V$ or                                            |                        | 0.8 | V     |

|                 |                                                                                                                                                                                                                                                         | V <sub>CC</sub> -0.1V                                          |                        |     |       |

| V <sub>OH</sub> | Minimum High Output Voltage                                                                                                                                                                                                                             | I <sub>OUT</sub> = -100 μA                                     | V <sub>CC</sub> - 0.2v |     | V     |

|                 | All Outputs and I/O Pins                                                                                                                                                                                                                                | $V_{IN} = V_{IH}$ or $V_{IL}$                                  |                        |     |       |

| V <sub>OH</sub> | Minimum High Output Voltage                                                                                                                                                                                                                             | I <sub>OUT</sub> = −12 mA                                      | 2.4                    |     | V     |

|                 | TDO <sub>B0</sub> , TDO <sub>B1</sub> , TRIST <sub>B0</sub> , TRIST <sub>B1</sub> , Y0 <sub>B0</sub> , Y1 <sub>B0</sub> , Y0 <sub>B1</sub> , Y1 <sub>B1</sub> , TDO <sub>(01-06)</sub> , Y0 <sub>01</sub> , Y1 <sub>01</sub> , TRIST <sub>(01-03)</sub> | All Outputs Loaded                                             |                        |     |       |

| V <sub>OH</sub> | Minimum High Output Voltage                                                                                                                                                                                                                             | I <sub>OUT</sub> = −24mA                                       | 2.2                    |     | V     |

|                 | $\begin{array}{l} TMS_{B0}, TMS_{B1}, TCK_{B\underline{0}}, \overline{TCK_{B1}}, \overline{TRST}_{B0}, \overline{TRST}_{B1}, \\ TMS_{(01-06)}, TCK_{(01-06)}, \overline{TRST}_{(01-06)} \end{array}$                                                    |                                                                |                        |     |       |

| V <sub>OL</sub> | Maximum Low Output Voltage                                                                                                                                                                                                                              | I <sub>OUT</sub> = +100 μA                                     |                        | 0.2 | V     |

|                 | All Outputs and I/O Pins                                                                                                                                                                                                                                | $I_{OUT} = +100 \mu A$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ |                        |     |       |

Product Folder Links: SCANSTA112

## DC ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified

| Symbol           | Parameter                                                                                                                                                                                                                                                                                | Conditions                                      | Min | Max  | Units |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----|------|-------|

| V <sub>OL</sub>  | Maximum Low Output Voltage                                                                                                                                                                                                                                                               | I <sub>OUT</sub> = +12 mA                       |     | 0.4  | V     |

|                  | $\begin{array}{c} TDO_{B0},TDO_{B1},TRIST_{B0},TRIST_{B1},Y0_{B0},Y1_{B0},Y0_{B1},\\ Y1_{B1},TDO_{(01-06)},Y0_{01},Y1_{01},TRIST_{(01-03)} \end{array}$                                                                                                                                  |                                                 |     |      |       |

| $V_{OL}$         | Maximum Low Output Voltage                                                                                                                                                                                                                                                               | $I_{OUT} = +24mA$                               |     | 0.55 | V     |

|                  | $\begin{array}{l} \text{TMS}_{B0}, \text{TMS}_{B1}, \text{TCK}_{B\underline{0}}, \overline{\text{TCK}}_{B1}, \overline{\text{TRST}}_{B0}, \overline{\text{TRST}}_{B1}, \\ \text{TMS}_{(01\text{-}06)}, \text{TCK}_{(01\text{-}06)}, \overline{\text{TRST}}_{(01\text{-}06)} \end{array}$ |                                                 |     |      |       |

| VIKL             | Maximum Input Clamp Diode Voltage                                                                                                                                                                                                                                                        | IIK = -18mA                                     |     | -1.2 | V     |

| I <sub>IN</sub>  | Maximum Input Leakage Current                                                                                                                                                                                                                                                            | $V_{IN} = V_{CC}$ or GND                        |     | ±5.0 | μA    |

|                  | (non-resistor input pins)                                                                                                                                                                                                                                                                |                                                 |     |      |       |

| $I_{ILR}$        | Input Current Low                                                                                                                                                                                                                                                                        | $V_{IN} = GND$                                  | -45 | -200 | μΑ    |

|                  | (Input and I/O pins with pull-up resistors: $TDI_{B0}$ , $TDI_{B1}$ , $TMS_{B0}$ , $TMS_{B1}$ , $\overline{TRST}_{B0}$ , $\overline{TRST}_{B1}$ , $A0_{B0}$ , $A1_{B0}$ , $A0_{B1}$ , $A1_{B1}$ , $TDI_{(01-06)}$ , $A0_{01}$ , $A1_{01}$ )                                              |                                                 |     |      |       |

| I <sub>IH</sub>  | Input High Current (Input and I/O pins with pull-up resistors: $TDI_{B0}$ , $TDI_{B1}$ , $TMS_{B0}$ , $TMS_{B1}$ , $\overline{TRST}_{B0}$ , $\overline{TRST}_{B1}$ , $A0_{B0}$ , $A1_{B0}$ , $A0_{B1}$ , $A1_{B1}$ , $TDI_{(01-06)}$ , $A0_{01}$ , $A1_{01}$ )                           | $V_{IN} = V_{CC}$                               |     | 5.0  | μА    |

| I <sub>OFF</sub> | Power-off Leakage Current Outputs and I/O pins without pull-up resistors                                                                                                                                                                                                                 | $V_{CC} = 0V, V_{IN} = 3.6V^{(1)}$              |     | ±5.0 | μA    |

|                  | Outputs and I/O pins with pull-up resistors                                                                                                                                                                                                                                              |                                                 |     | ±200 | μΑ    |

| I <sub>OZ</sub>  | Maximum TRI-STATE Leakage Current                                                                                                                                                                                                                                                        |                                                 |     | ±5.0 | μA    |

|                  | Outputs and I/O pins without pull-up resistors                                                                                                                                                                                                                                           |                                                 |     |      |       |

| I <sub>CC</sub>  | Maximum Quiescent Supply Current                                                                                                                                                                                                                                                         | $V_{IN} = V_{CC}$ or GND                        |     | 3.8  | mA    |

| I <sub>CCD</sub> | Maximum Dynamic Supply Current                                                                                                                                                                                                                                                           | $V_{IN} = V_{CC}$ or GND, Input<br>Freq = 25MHz |     | 68   | mA    |

<sup>(1)</sup> Specified by equivalent test method.

## AC ELECTRICAL CHARACTERISTICS: SCAN BRIDGE MODE

Over recommended operating supply voltage and temperature ranges unless otherwise specified (1).

| Symbol             | Parameter                                                   | Conditions | Тур | Max  | Units |

|--------------------|-------------------------------------------------------------|------------|-----|------|-------|

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.5 | 13.5 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TDO <sub>B0</sub> or TDO <sub>B1</sub> |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.5 | 14.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B1</sub> to TDO <sub>B0</sub> or TDO <sub>B1</sub> |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 7.5 | 12.5 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TDO <sub>(01-06)</sub>                 |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 7.5 | 13.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B1</sub> to TDO <sub>(01-06)</sub>                 |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.0 | 12.0 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B0</sub> to TMS <sub>B1</sub>                      |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.0 | 12.0 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B1</sub> to TMS <sub>B0</sub>                      |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.0 | 12.0 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B0</sub> to TMS <sub>(01-06)</sub>                 |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.0 | 12.0 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B1</sub> to TMS <sub>(01-06)</sub>                 |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                           |            | 8.0 | 12.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TCK <sub>B1</sub>                      |            |     |      |       |

Product Folder Links: SCANSTA112

(1)  $R_L = 500\Omega$  to GND,  $C_L = 50 pF$  to GND,  $t_R/t_F = 2.5 ns$ , Frequency = 25MHz,  $V_M = 1.5 V$

## AC ELECTRICAL CHARACTERISTICS: SCAN BRIDGE MODE (continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified<sup>(1)</sup>.

| Symbol             | Parameter                                                        | Conditions | Тур  | Max  | Units |

|--------------------|------------------------------------------------------------------|------------|------|------|-------|

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 8.0  | 12.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B1</sub> to TCK <sub>B0</sub>                           |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 7.5  | 12.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TCK <sub>(01-06)</sub>                      |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 7.5  | 12.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B1</sub> to TCK <sub>(01-06)</sub>                      |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 11.5 | 18.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TRST <sub>B1</sub>                          |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 11.5 | 18.0 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B1</sub> to TRST <sub>B0</sub>                          |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 12.0 | 18.5 | ns    |

| t <sub>PLH</sub>   | TCK <sub>B0</sub> to TRST <sub>(01-06)</sub>                     |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 12.0 | 18.5 | ns    |

| t <sub>PLH</sub>   | $TCK_{B1}$ to $\overline{TRST}_{(01-06)}$                        |            |      |      |       |

| t <sub>PHL</sub>   | Propagation Delay                                                |            | 8.5  | 12.5 | ns    |

|                    | TCK <sub>Bn</sub> to TRIST <sub>Bn</sub>                         |            |      |      |       |

| t <sub>PHL</sub>   | Propagation Delay                                                |            | 8.0  | 12.0 | ns    |

|                    | TCK <sub>Bn</sub> to TRIST <sub>(01-03)</sub>                    |            |      |      |       |

| t <sub>PZL</sub> , | Propagation Delay                                                |            | 9.0  | 14.5 | ns    |

| t <sub>PZH</sub>   | TCK <sub>Bn</sub> to TDO <sub>Bn</sub> or TDO <sub>(01-06)</sub> |            |      |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                |            | 6.0  | 9.0  | ns    |

| t <sub>PLH</sub>   | An to Yn                                                         |            |      |      |       |

## **AC TIMING CHARACTERISTICS: SCAN BRIDGE MODE**

Over recommended operating supply voltage and temperature ranges unless otherwise specified (1)(2).

| Symbol         | Parameter                                   | Conditions | Min | Max | Units |

|----------------|---------------------------------------------|------------|-----|-----|-------|

| t <sub>S</sub> | Setup Time                                  |            | 2.5 |     |       |

|                | TMS <sub>Bn</sub> to TCK <sub>Bn</sub>      |            |     |     | ns    |

| t <sub>H</sub> | Hold Time                                   |            | 1.5 |     |       |

|                | TMS <sub>Bn</sub> to TCK <sub>Bn</sub>      |            |     |     | ns    |

| t <sub>S</sub> | Setup Time                                  |            | 3.0 |     |       |

|                | TDI <sub>Bn</sub> to TCK <sub>Bn</sub>      |            |     |     | ns    |

| t <sub>H</sub> | Hold Time                                   |            | 2.0 |     | 200   |

|                | TDI <sub>Bn</sub> to TCK <sub>Bn</sub>      |            |     |     | ns    |

| t <sub>S</sub> | Setup Time                                  |            | 1.0 |     | 20    |

|                | TDI <sub>(01-06)</sub> to TCK <sub>Bn</sub> |            |     |     | ns    |

| t <sub>H</sub> | Hold Time                                   |            | 3.5 |     |       |

|                | TDI <sub>(01-06)</sub> to TCK <sub>Bn</sub> |            |     |     | ns    |

Copyright © 2002–2013, Texas Instruments Incorporated

<sup>(1)</sup> Specified by Design (GBD) by statistical analysis (2)  $R_L = 500\Omega$  to GND,  $C_L = 50$ pF to GND,  $t_R/t_F = 2.5$ ns, Frequency = 25MHz,  $V_M = 1.5$ V

## AC TIMING CHARACTERISTICS: SCAN BRIDGE MODE (continued)

Over recommended operating supply voltage and temperature ranges unless otherwise specified<sup>(1)(2)</sup>.

| Symbol           | Parameter                                 | Conditions         | Min  | Max | Units |

|------------------|-------------------------------------------|--------------------|------|-----|-------|

| t <sub>REC</sub> | Recovery Time                             |                    | 1.0  |     | 20    |

|                  | TCK <sub>Bn</sub> from TRST <sub>Bn</sub> |                    |      |     | ns    |

| t <sub>W</sub>   | Clock Pulse Width                         | $t_R/t_F = 1.0$ ns | 10.0 |     | ns    |

|                  | TCK <sub>Bn</sub> (H or L)                |                    |      |     |       |

| t <sub>W</sub> L | Reset Pulse Width                         | $t_R/t_F = 1.0$ ns | 2.5  |     | ns    |

|                  | TRST <sub>Bn</sub> (L)                    |                    |      |     |       |

| F <sub>MAX</sub> | Maximum Clock Frequency <sup>(3)</sup>    | $t_R/t_F = 1.0$ ns | 25   |     | MHz   |

<sup>(3)</sup> When sending vectors one-way to a target device on an LSP (such as in FPGA/PLD configuration/programming), the clock frequency may be increased above this specification. In Scan Mode (expecting to capture returning data at the LSP), the F<sub>MAX</sub> must be limited to the above specification.

### AC ELECTRICAL CHARACTERISTICS: STITCHER TRANSPARENT MODE

Over recommended operating supply voltage and temperature ranges unless otherwise specified (1).

| Symbol             | Parameter                                                                                                     | Conditions | Тур | Max  | Units |

|--------------------|---------------------------------------------------------------------------------------------------------------|------------|-----|------|-------|

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | $TDI_{B0}$ to $TDO_{B1}$ , $TDI_{B1}$ to $TDO_{B0}$                                                           |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | TDI <sub>B0</sub> to TDO <sub>01</sub> , TDI <sub>B1</sub> to TDO <sub>01</sub>                               |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | TDI <sub>LSPn</sub> to TDO <sub>LSPn+1</sub>                                                                  |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B0</sub> to TMS <sub>B1</sub> , TMS <sub>B1</sub> to TMS <sub>B0</sub>                               |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | TMS <sub>B0</sub> to TMS <sub>(01-06)</sub> , TMS <sub>B1</sub> to TMS <sub>(01-06)</sub>                     |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | $\overline{TRST}_{B0}$ to $\overline{TRST}_{B1}$ , $\overline{TRST}_{B1}$ to $\overline{TRST}_{B0}$           |            |     |      |       |

| t <sub>PHL</sub> , | Propagation Delay                                                                                             |            |     | 12.5 | ns    |

| t <sub>PLH</sub>   | $\overline{TRST}_{B0}$ to $\overline{TRST}_{(01-06)}$ , $\overline{TRST}_{B1}$ to $\overline{TRST}_{(01-06)}$ |            |     |      |       |

(1)  $R_L = 500\Omega$  to GND,  $C_L = 50$ pF to GND,  $t_R/t_F = 2.5$ ns, Frequency = 25MHz,  $V_M = 1.5$ V

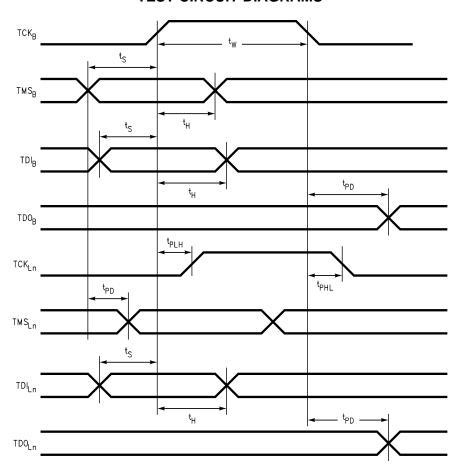

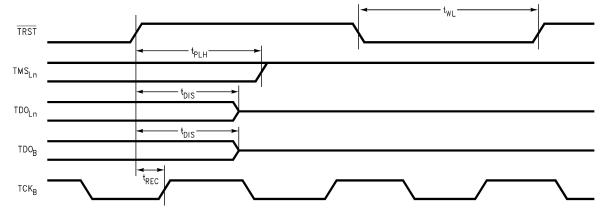

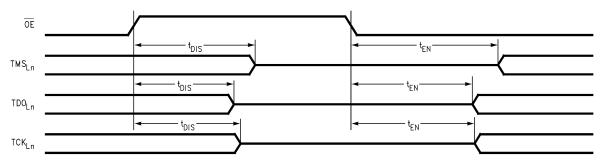

## **TEST CIRCUIT DIAGRAMS**

Figure 6. Waveforms for an Unparked STA112 in the Shift-DR (IR) TAP Controller State

Figure 7. Reset Waveforms

Figure 8. Output Enable Waveforms

# Capacitance & I/O Characteristics

Refer to TI's website for IBIS models at www.ti.com.com/lsds/ti/analog/interface.page

## **REVISION HISTORY**

| CI | Changes from Revision H (April 2013) to Revision I |  |    |  |  |  |

|----|----------------------------------------------------|--|----|--|--|--|

| •  | Changed layout of National Data Sheet to TI format |  | 14 |  |  |  |

Product Folder Links: SCANSTA112

www.ti.com 14-May-2024

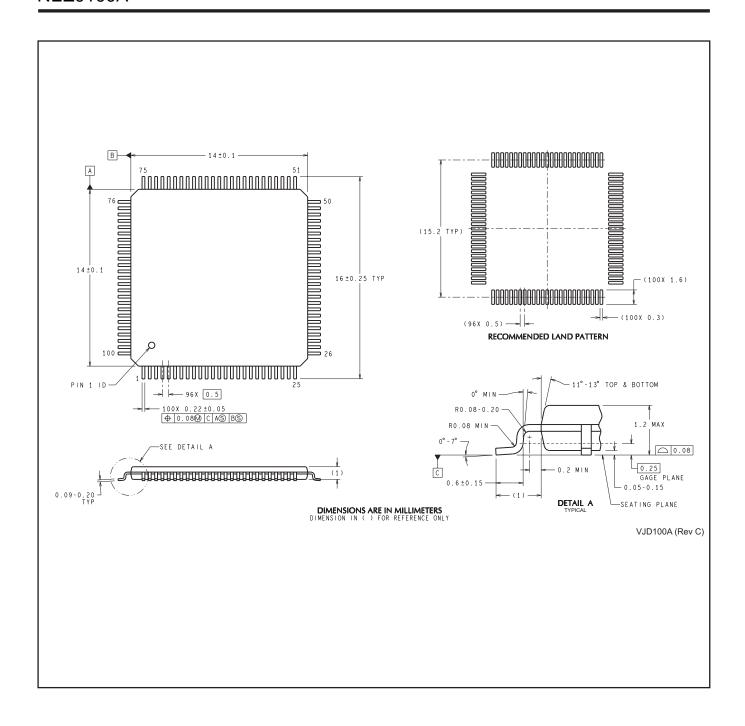

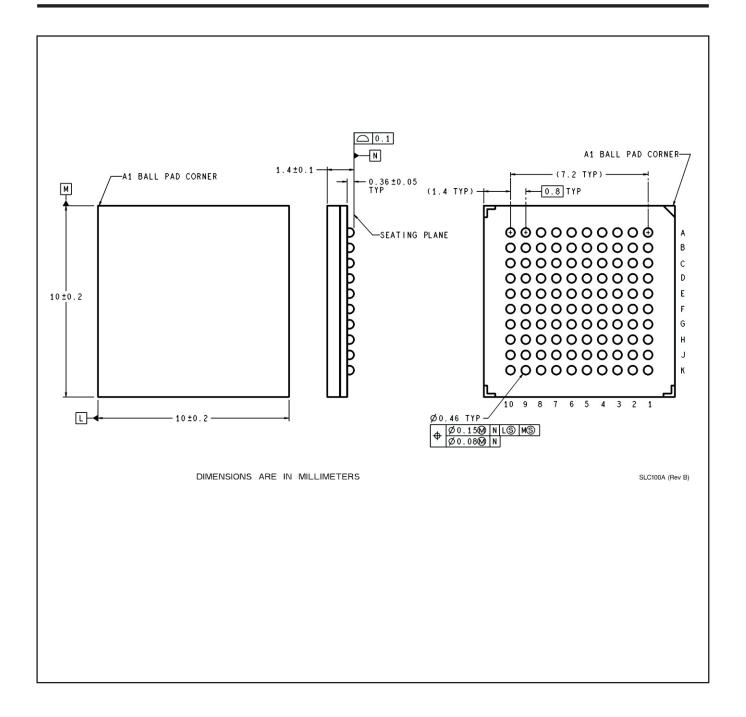

#### PACKAGING INFORMATION

| Orderable Device   | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|--------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| SCANSTA112SM       | ACTIVE     | NFBGA        | NZD                | 100  | 240            | Non-RoHS<br>& Green | Call TI                       | Level-3-235C-168 HR | -40 to 85    | SCANSTA112<br>SM        | Samples |

| SCANSTA112SM/NOPB  | ACTIVE     | NFBGA        | NZD                | 100  | 240            | RoHS & Green        | SNAGCU                        | Level-4-260C-72 HR  | -40 to 85    | SCANSTA112<br>SM        | Samples |

| SCANSTA112SMX      | NRND       | NFBGA        | NZD                | 100  | 1000           | Non-RoHS<br>& Green | Call TI                       | Level-3-235C-168 HR | -40 to 85    | SCANSTA112<br>SM        |         |

| SCANSTA112SMX/NOPB | ACTIVE     | NFBGA        | NZD                | 100  | 1000           | RoHS & Green        | SNAGCU                        | Level-4-260C-72 HR  | -40 to 85    | SCANSTA112<br>SM        | Samples |

| SCANSTA112VS/NOPB  | ACTIVE     | TQFP         | NEZ                | 100  | 90             | RoHS & Green        | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | SCANSTA112<br>VS        | Samples |

| SCANSTA112VSX/NOPB | ACTIVE     | TQFP         | NEZ                | 100  | 1000           | RoHS & Green        | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | SCANSTA112<br>VS        | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 14-May-2024

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-May-2024

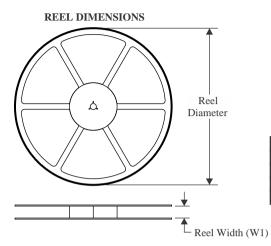

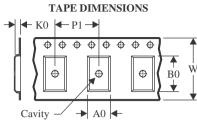

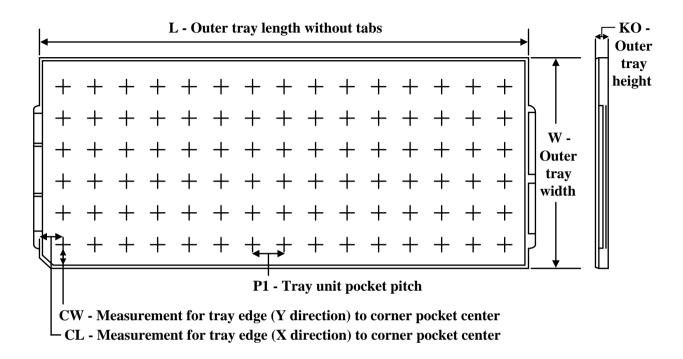

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

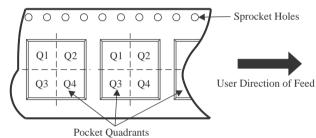

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device             | Package<br>Type | Package<br>Drawing |     | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------------|-----------------|--------------------|-----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SCANSTA112SMX      | NFBGA           | NZD                | 100 | 1000 | 330.0                    | 24.4                     | 10.3       | 10.3       | 2.0        | 16.0       | 24.0      | Q1               |

| SCANSTA112SMX/NOPB | NFBGA           | NZD                | 100 | 1000 | 330.0                    | 24.4                     | 10.3       | 10.3       | 2.0        | 16.0       | 24.0      | Q1               |

| SCANSTA112VSX/NOPB | TQFP            | NEZ                | 100 | 1000 | 330.0                    | 32.4                     | 18.0       | 18.0       | 1.6        | 24.0       | 32.0      | Q2               |

www.ti.com 11-May-2024

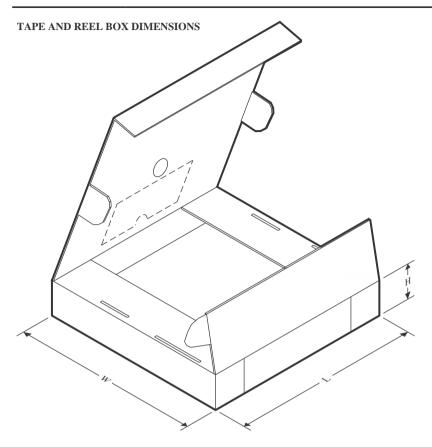

### \*All dimensions are nominal

| Device             | Device Package Type |     | Pins SPQ |      | Length (mm) | Width (mm) | Height (mm) |  |  |  |  |

|--------------------|---------------------|-----|----------|------|-------------|------------|-------------|--|--|--|--|

| SCANSTA112SMX      | NFBGA               | NZD | 100      | 1000 | 356.0       | 356.0      | 45.0        |  |  |  |  |

| SCANSTA112SMX/NOPB | NFBGA               | NZD | 100      | 1000 | 356.0       | 356.0      | 45.0        |  |  |  |  |

| SCANSTA112VSX/NOPB | TQFP                | NEZ | 100      | 1000 | 367.0       | 367.0      | 55.0        |  |  |  |  |

www.ti.com 11-May-2024

## **TRAY**

Chamfer on Tray corner indicates Pin 1 orientation of packed units.

#### \*All dimensions are nominal

| Device            | Package<br>Name | Package<br>Type | Pins | SPQ | Unit array<br>matrix | Max<br>temperature<br>(°C) | L (mm) | W<br>(mm) | Κ0<br>(μm) | P1<br>(mm) | CL<br>(mm) | CW<br>(mm) |

|-------------------|-----------------|-----------------|------|-----|----------------------|----------------------------|--------|-----------|------------|------------|------------|------------|

| SCANSTA112SM      | NZD             | NFBGA           | 100  | 240 | 10 X 24              | 150                        | 322.6  | 135.9     | 7620       | 12.4       | 14.9       | 12.15      |

| SCANSTA112SM/NOPB | NZD             | NFBGA           | 100  | 240 | 10 X 24              | 150                        | 322.6  | 135.9     | 7620       | 12.4       | 14.9       | 12.15      |

| SCANSTA112VS      | NEZ             | TQFP            | 100  | 90  | 6 X 15               | 150                        | 322.6  | 135.9     | 7620       | 20.3       | 15.4       | 15.45      |

| SCANSTA112VS/NOPB | NEZ             | TQFP            | 100  | 90  | 6 x 15               | 150                        | 322.6  | 135.9     | 7620       | 20.3       | 15.4       | 15.45      |

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated