Click here to ask an associate for production status of specific part numbers.

## **Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability**

#### MAX16050/MAX16051

#### **General Description**

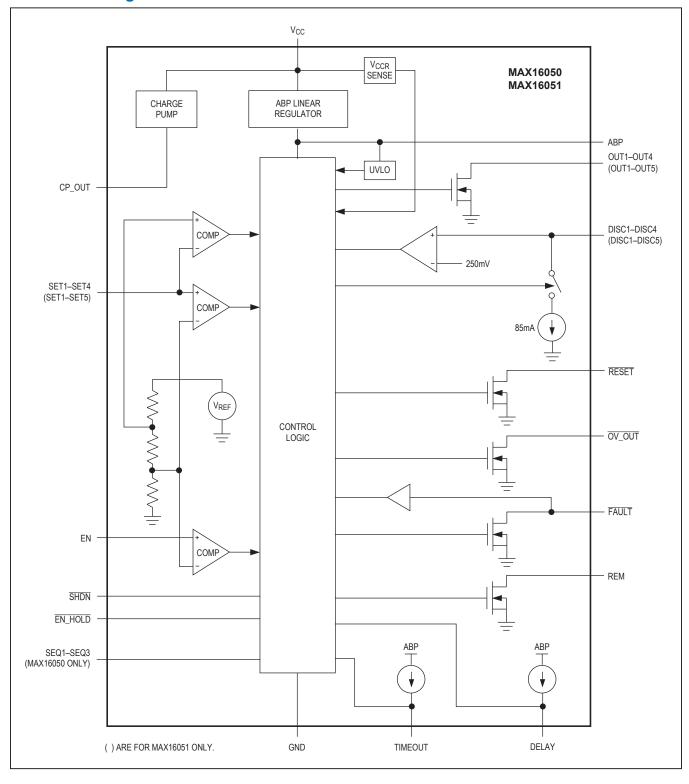

The MAX16050 monitors up to 5 voltages and sequences up to 4 voltages, while the MAX16051 monitors up to 6 voltages and sequences up to 5 voltages. These devices provide an adjustable delay as each supply is turned on and they monitor each power-supply voltage, including the input voltage V<sub>CC</sub>. When all of the voltages reach their final values and the reset delay timer expires, a power-on-reset (RESET) output deasserts allowing the microcontroller (µC) to operate. If any voltage falls below its threshold, the reset output asserts and all voltage supplies are turned off. The MAX16050/MAX16051 can be daisy-chained to control a higher number of voltages in a system.

During a power-down event, the MAX16050/MAX16051 can reverse sequence the outputs. In this situation, each voltage is turned off sequentially until it reaches a 250mV level, at which point, the next supply is turned off. The MAX16050/MAX16051 also provide internal pulldown circuitry that turns on during power-down, to help discharge large output capacitors.

The MAX16050/MAX16051 feature a charge-pump supply output that can be used as a pullup voltage for driving external n-channel MOSFETs and an overvoltage output that indicates when any of the monitored voltages exceeds its overvoltage threshold. The MAX16050 also provides three sequence control inputs for changing the sequence order, while the MAX16051 has a fixed sequence order.

The MAX16050/MAX16051 are available in a 28-pin (4mm x 4mm) thin QFN package and are fully specified over the -40°C to +85°C extended operating temperature range.

#### **Applications**

- Servers

- Workstations

- **Networking Systems**

- Telecom Equipment

- Storage Systems

#### **Features**

- Monitor Up to 6 Voltages/Sequence Up to 5 Voltages (MAX16051)

- Pin-Selectable Sequencing Order (MAX16050 Only)

- Reverse-Sequencing Capability on Shutdown

- Overvoltage Monitoring with Independent Output

- ±1.5% Threshold Accuracy

- 2.7V to 16V Operating Voltage Range

- Charge Pump to Fully Enhance External n-Channel FETs

- Capacitor-Adjustable Sequencing Delay

- Fixed or Capacitor-Adjustable Reset Timeout

- Internal 85mA Pulldowns for Discharging Capacitive Loads Quickly

- Daisy-Chaining Capability to Communicate Across Multiple Devices

- Small 4mm x 4mm, 28-Pin TQFN Package

Ordering Information and Typical Operating Circuit appears at end of data sheet.

# Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

## **Absolute Maximum Ratings**

| (All voltages referenced to GND.)     |                                |

|---------------------------------------|--------------------------------|

| V <sub>CC</sub>                       | 0.3V to +30V                   |

| REM, OUT_, DISC                       |                                |

| RESET, SHDN, SET_, FAULT, EN_HOLD     | , EN, DELAY,                   |

| OV_OUT, ABP, TIMEOUT, SEQ             | 0.3V to +6V                    |

| CP_OUT                                | 0.3V to (V <sub>CC</sub> + 6V) |

| RESET Current                         | 50mA                           |

| DISC_ Current                         | 180mA                          |

| Input/Output Current (all other pins) | 20mA                           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| 28-Pin (4mm x 4mm) Thin QFN (derate 28.6              | SmW/°C          |

| above +70°C)                                          | 2285mW*         |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | -65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C          |

| Soldering Temperature (reflow)                        | +260°C          |

| *As per JEDEC51 Standard (Multilayer Board)           |                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(V_{CC} = 2.7V \text{ to } 16V, V_{EN} = V_{ABP}, T_A = T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                           | SYMBOL                | CONDITIONS                                                                                          | MIN   | TYP  | MAX   | UNITS               |

|-------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|-------|------|-------|---------------------|

| Operating Voltage Range             | V <sub>CC</sub>       | Voltage on V <sub>CC</sub> to ensure the device is fully operational                                |       |      | 16    | V                   |

| Reset Voltage (Note 2)              | V <sub>CCR</sub>      | V <sub>DISC</sub> = V <sub>OUT</sub> = V <sub>RESET</sub> = low, voltage on V <sub>CC</sub> falling |       |      | 1.1   | V                   |

| Regulated Supply Voltage            | V <sub>ABP</sub>      | I <sub>ABP</sub> = 1mA (external sourcing current from ABP)                                         | 2.45  |      | 2.90  | V                   |

| Undervoltage Lockout                | V <sub>UVLO</sub>     | Minimum voltage on ABP, ABP rising                                                                  |       | 2.3  |       | V                   |

| Undervoltage Lockout Hysteresis     | V <sub>UVLO_HYS</sub> | ABP falling                                                                                         |       | 100  |       | mV                  |

| Supply Current                      | ICC                   | V <sub>CC</sub> = 3.3V, all OUT_ = high, no load                                                    |       | 0.7  | 1.4   | mA                  |

| MONITORED ANALOG INPUTS             |                       |                                                                                                     |       |      |       |                     |

| SET_ Threshold                      | V <sub>TH</sub>       | SET_ falling                                                                                        | 0.492 | 0.5  | 0.508 | V                   |

| SET_ Threshold Hysteresis           | V <sub>TH_HYS</sub>   | SET_ rising                                                                                         |       | 0.5  |       | %V <sub>TH</sub>    |

| SET1-SET4 Input Current             | I <sub>SET</sub>      | V <sub>SET</sub> _ = 0.5V                                                                           | -100  |      | +100  | nA                  |

| SET5 Input Current                  | I <sub>SET5</sub>     | V <sub>SET5</sub> = 0.5V (MAX16051 only)                                                            | -100  |      | +100  | nA                  |

| SET_ Threshold Tempco               | ΔV <sub>TH/_TC</sub>  |                                                                                                     |       | 30   |       | ppm/°C              |

| Overvoltage Threshold               | V <sub>TH_OV</sub>    | SET_ rising                                                                                         | 0.541 | 0.55 | 0.558 | V                   |

| Overvoltage Threshold<br>Hysteresis |                       | SET_ falling                                                                                        |       | 0.5  |       | %V <sub>TH_OV</sub> |

| EN Threshold                        | V <sub>TH_EN</sub>    | EN_ falling                                                                                         | 0.492 | 0.5  | 0.508 | V                   |

| EN Threshold Hysteresis             | V <sub>EN_HYS</sub>   | EN_ rising                                                                                          |       | 0.5  |       | %V <sub>TH_EN</sub> |

| EN Pulse Width                      | t <sub>ENLO_PW</sub>  | EN falling                                                                                          | 25    |      |       | μs                  |

| EN to OUT_ Delay                    | t <sub>ENLO_OUT</sub> | EN falling                                                                                          |       | 30   |       | μs                  |

| EN Input Current                    | I <sub>EN</sub>       | V <sub>EN</sub> = 0.5V                                                                              | -100  |      | +100  | nA                  |

# Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

## **Electrical Characteristics (continued)**

$(V_{CC} = 2.7V \text{ to } 16V, V_{EN} = V_{ABP}, T_A = T_J = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                             | SYMBOL                | CONDITIONS                                                                           | MIN                     | TYP   | MAX   | UNITS |  |

|-------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|-------------------------|-------|-------|-------|--|

| SEQUENCING, CAPACITOR DIS                             | CHARGE, AN            | D SEQUENCE TIMING OUTPUTS                                                            |                         |       |       |       |  |

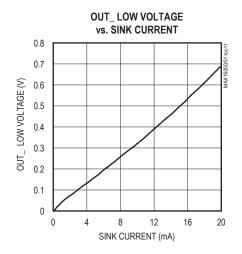

| OUT Outside and the                                   | .,,                   | V <sub>CC</sub> = 3.3V, I <sub>SINK</sub> = 3.2mA                                    |                         |       | 0.3   |       |  |

| OUT_ Output Low Voltage                               | V <sub>OL</sub> OUT   | V <sub>CC</sub> = 1.8V, I <sub>SINK</sub> = 100μA                                    |                         |       | 0.3   | V     |  |

| OUT_ Leakage Current                                  | I <sub>LKG_OUT</sub>  | V <sub>OUT</sub> _ = 12V, OUT_ asserted                                              |                         |       | 1     | μΑ    |  |

| DISC_ Output Pulldown Current                         | I <sub>OL_DISC</sub>  | Pulldown current during fault condition or power-down mode, V <sub>DISC</sub> _ = 1V |                         | 85    |       | mA    |  |

| DISC_ Output Leakage Current                          | I <sub>LKG_DISC</sub> | V <sub>DISC</sub> = 3.3V, not in power-down mode                                     |                         |       | 1     | μA    |  |

| DISC_ Power Low Threshold                             | V <sub>TH_PL</sub>    | DISC_ falling                                                                        | 200                     | 250   | 300   | mV    |  |

| DELAY, TIMEOUT Output Source Current                  | I <sub>DT</sub>       | V <sub>DELAY</sub> = V <sub>TIMEOUT</sub> = 0V                                       | 1.6                     | 2.5   | 3.0   | μA    |  |

| DELAY, TIMEOUT Threshold<br>Voltage                   | V <sub>TH_DT</sub>    |                                                                                      | 1.218                   | 1.250 | 1.281 | V     |  |

| DIGITAL INPUTS/OUTPUTS                                |                       |                                                                                      |                         |       |       |       |  |

| SHDN, FAULT, EN_HOLD Input-<br>Logic Low Voltage      | V <sub>IL</sub>       |                                                                                      |                         |       | 0.4   | V     |  |

| SHDN, FAULT, EN_HOLD Input-<br>Logic High Voltage     | V <sub>IH</sub>       |                                                                                      | 2                       |       |       | V     |  |

| EN_HOLD Input Current                                 | II                    |                                                                                      |                         |       | 1     | μΑ    |  |

| EN_HOLD to OUT_ Delay                                 | t <sub>EN_OUT</sub>   |                                                                                      |                         | 3     |       | μs    |  |

| FAULT, SHDN to ABP Pullup<br>Resistance               | R <sub>P</sub>        |                                                                                      | 60                      | 100   | 160   | kΩ    |  |

| SHDN to OUT_ Delay                                    | tout                  |                                                                                      |                         | 12    |       | μs    |  |

| SHDN to Pulse Width                                   | t <sub>SHDN_PW</sub>  | SHDN falling                                                                         | 1.9                     |       |       | μs    |  |

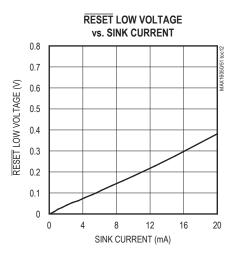

| RESET Output Low Voltage                              | .,                    | V <sub>CC</sub> = 3.3V, I <sub>SINK</sub> = 3.2mA                                    | 0.3                     |       | 0.3   | V     |  |

| NESET Output Low Voltage                              | VOL                   | V <sub>CC</sub> = 1.8V, I <sub>SINK</sub> = 100μA                                    |                         |       | 0.3   | V     |  |

| REM, FAULT Output Low Voltage                         | V <sub>OL_RF</sub>    | V <sub>CC</sub> = 3.3V, I <sub>SINK</sub> = 3.2mA                                    |                         |       | 0.3   | V     |  |

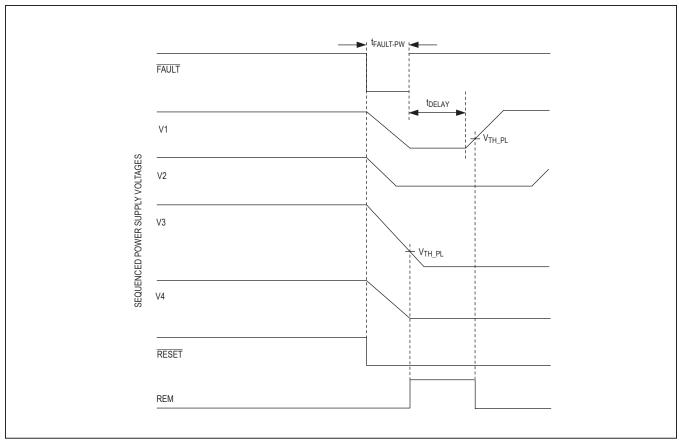

| FAULT Pulse Width                                     | tFAULT_PW             | FAULT falling                                                                        | 1.9                     |       |       | μs    |  |

| SET_ to FAULT Delay Time                              | tSET_FAULT            | SET_ falling below respective threshold                                              |                         | 2.5   |       | μs    |  |

| SEQ1-SEQ3 Logic-High Level                            | V <sub>IH_SEQ</sub>   | MAX16050 only                                                                        | V <sub>ABP</sub> - 0.35 |       |       | V     |  |

| SEQ1-SEQ3 Logic High-<br>Impedance (No Connect) Level | V <sub>IX_SEQ</sub>   | MAX16050 only                                                                        | 0.92                    |       | 1.45  | V     |  |

| SEQ1-SEQ3 Logic-Low Level                             | V <sub>IL_SEQ</sub>   | MAX16050 only                                                                        |                         |       | 0.33  | V     |  |

| SEQ1–SEQ3 High-Impedance<br>State Tolerance Current   | IIX                   | MAX16050 (Note 3)                                                                    | -6                      |       | +6    | μA    |  |

#### **Electrical Characteristics (continued)**

(V<sub>CC</sub> = 2.7V to 16V, V<sub>EN</sub> = V<sub>ABP</sub>, T<sub>A</sub> = T<sub>J</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

| PARAMETER                         | SYMBOL              | CONDITIONS                                                                           |                       | TYP                    | MAX                   | UNITS |  |

|-----------------------------------|---------------------|--------------------------------------------------------------------------------------|-----------------------|------------------------|-----------------------|-------|--|

| RESET CIRCUIT                     |                     |                                                                                      |                       |                        |                       |       |  |

| RESET, REM, OV_OUT Output Leakage | I <sub>LKG</sub>    | $V_{\overline{RESET}} = V_{\overline{REM}} = V_{\overline{OV}\_\overline{OUT}} = 5V$ |                       |                        | 1                     | μΑ    |  |

| RESET Timeout Period              | t <sub>RP</sub>     | TIMEOUT = ABP                                                                        | 50                    | 128                    | 300                   | ms    |  |

| OUT_, FAULT, SHDN to RESET Delay  | t <sub>RST</sub>    | TIMEOUT = unconnected                                                                | 3                     |                        | μs                    |       |  |

| CHARGE-PUMP OUTPUT                | CHARGE-PUMP OUTPUT  |                                                                                      |                       |                        |                       |       |  |

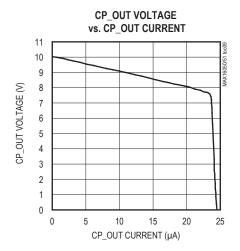

| CP_OUT Voltage                    | V <sub>CP_OUT</sub> | I <sub>CP_OUT</sub> = 0.5μA                                                          | V <sub>CC</sub> + 4.6 | V <sub>CC</sub><br>+ 5 | V <sub>CC</sub> + 5.8 | V     |  |

| CP_OUT Source Current             | I <sub>CP_OUT</sub> | V <sub>CP_OUT</sub> = V <sub>CC</sub> + 2V                                           | 17                    | 25                     | 30                    | μΑ    |  |

Note 1: Specifications are guaranteed for the stated global conditions, unless otherwise noted. 100% production tested at  $T_A = +25^{\circ}\text{C}$  and  $T_A = +85^{\circ}\text{C}$ . Specifications at  $T_A = -40^{\circ}\text{C}$  are guaranteed by design.

Note 2: V<sub>CCR</sub> is the lowest V<sub>CC</sub> for which DISC\_, OUT\_, and RESET are guaranteed to be low. See Reset Voltage V<sub>CCR</sub> section under *Detailed Description*.

Note 3: SEQ1-SEQ3 are inputs with three logic levels: high, low, and high-impedance.

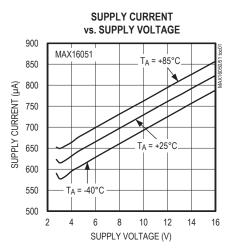

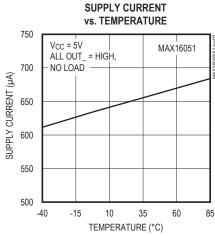

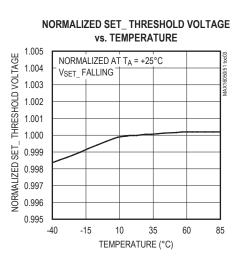

### **Typical Operating Characteristics**

(V<sub>CC</sub> = 5V; V<sub>EN</sub> = V<sub>ABP</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 5V; V<sub>EN</sub> = V<sub>ABP</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 5V; V<sub>EN</sub> = V<sub>ABP</sub>, T<sub>A</sub> = +25°C, unless otherwise noted.)

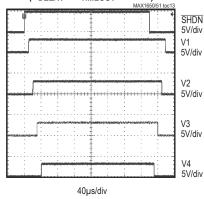

## REVERSE SEQUENCE POWER-DOWN USING SHDN (CDELAY = CTIMEOUT = OPEN)

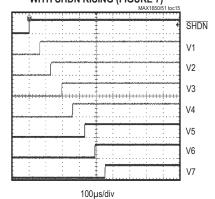

DAISY-CHAINING TWO DEVICES WITH SHDN RISING (FIGURE 7)

$\frac{C_{DELAY}}{SHDN}$  (U1) =  $C_{DELAY}$  (U2) = 100pF  $\frac{SHDN}{SHDN}$  = 5V/div V1–V7 = 5V/div

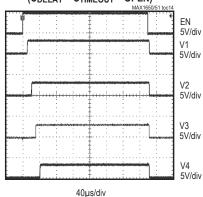

SIMULTANEOUS POWER-DOWN USING EN (CDELAY = CTIMEOUT = OPEN)

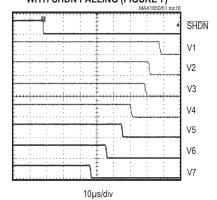

DAISY-CHAINING TWO DEVICES WITH SHDN FALLING (FIGURE 7)

C<sub>DELAY</sub> (U1) = C<sub>DELAY</sub> (U2) = 100pF SHDN = 5V/div V1-V7 = 5V/div

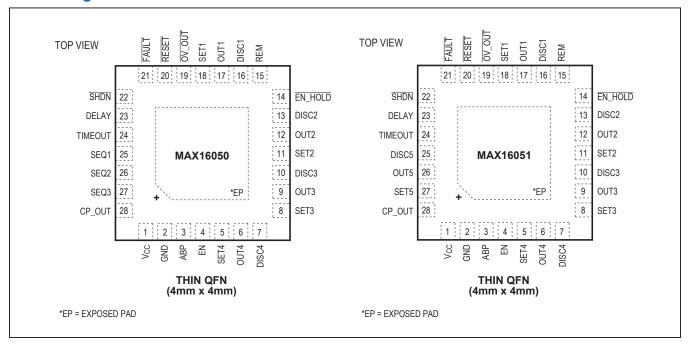

## **Pin Configurations**

## **Pin Description**

| PI       | PIN      |          | FUNCTION                                                                                                                                                                                                         |  |  |  |

|----------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX16050 | MAX16051 | NAME     | FUNCTION                                                                                                                                                                                                         |  |  |  |

| 1        | 1        | $V_{CC}$ | Device Power-Supply Input. Connect to 2.7V to 16V. Bypass $V_{CC}$ to GND with a 0.1 $\mu$ F capacitor.                                                                                                          |  |  |  |

| 2        | 2        | GND      | Ground                                                                                                                                                                                                           |  |  |  |

| 3        | 3        | ABP      | Internal Supply Bypass Input. Connect a 1µF capacitor from ABP to GND. ABP is an internally generated voltage powering internal circuits, and supply more than 1mA additional current to any external circuitry. |  |  |  |

| 4        | 4        | EN       | Analog Enable Input. Connect a resistive divider at EN to monitor a voltage. The EN threshold is 0.5V.                                                                                                           |  |  |  |

| 5        | 5        | SET4     | Set Monitored Threshold 4 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET4 threshold is 0.5V. It is recommended to have an input slew rate of 1V/15ms or faster.   |  |  |  |

| 6        | 6        | OUT4     | Open-Drain Output 4. When the voltage at SET3* is above 0.5V, OUT4 goes high impedance. OUT4 requires an external pullup resistor and can be pulled up to $V_{CC}$ .                                             |  |  |  |

| 7        | 7        | DISC4    | Discharge Pulldown Input 4. During normal operation, DISC4 is high impedance. During a fault condition or power-down, DISC4 provides an 85mA sink current.                                                       |  |  |  |

| 8        | 8        | SET3     | Set Monitored Threshold 3 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET3 threshold is 0.5V. It is recommended to have an input slew rate of 1V/15ms or faster.   |  |  |  |

| 9        | 9        | OUT3     | Open-Drain Output 3. When the voltage at SET2* is above 0.5V, OUT3 goes high impedance. OUT3 requires an external pullup resistor and can be pulled up to V <sub>CC</sub> .                                      |  |  |  |

<sup>\*</sup>This applies to the MAX16051. For the MAX16050, see <u>Table 1</u> for the output sequence order.

# Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

## **Pin Description (continued)**

| PIN      |          |         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|----------|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MAX16050 | MAX16051 | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 10       | 10       | DISC3   | Discharge Pulldown Input 3. During normal operation, DISC3 is high impedance. During a fault condition or power-down, DISC3 provides an 85mA sink current.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 11       | 11       | SET2    | Set Monitored Threshold 2 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET2 threshold is 0.5V. It is recommended to have an input slew rate of 1V/15ms or faster.                                                                                                                                                                                                                                               |  |  |  |

| 12       | 12       | OUT2    | Open-Drain Output 2. When the voltage at SET1* is above 0.5V, OUT2 goes high impedance. OUT2 requires an external pullup resistor and can be pulled up to $V_{CC}$ .                                                                                                                                                                                                                                                                                         |  |  |  |

| 13       | 13       | DISC2   | Discharge Pulldown Input 2. During normal operation, DISC2 is high impedance. During a fault condition or power-down, DISC2 provides an 85mA sink current.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 14       | 14       | EN_HOLD | Enable Hold Input. When $\overline{\text{EN\_HOLD}}$ is low, the device does not start the reverse-sequencing process regardless of the status of the $\overline{\text{SHDN}}$ input. Reverse sequencing is allowed when this input is pulled high. Connect to ABP if unused.                                                                                                                                                                                |  |  |  |

| 15       | 15       | REM     | Open-Drain Bus Removal Output. REM goes high impedance when all DISC_ inputs are below the DISC_ power low threshold ( $V_{TH\_PL}$ ). REM goes low when any DISC_ input goes above $V_{TH\_PL}$ . REM requires an external pullup resistor and can be pulled up to $V_{CC}$ .                                                                                                                                                                               |  |  |  |

| 16       | 16       | DISC1   | Discharge Pulldown Input 1. During normal operation, DISC1 is high impedance. During a fault condition or power-down, DISC1 provides an 85mA sink current.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 17       | 17       | OUT1    | Open-Drain Output 1. OUT1 goes high impedance, when the following startup conditions are met*: $V_{ABP} > V_{UVLO}$ , $V_{EN} > V_{TH\_EN}$ , SHDN not asserted, and DISC_ voltages < 250mV. OUT1 requires an external pullup resistor and can be pulled up to $V_{CC}$ .                                                                                                                                                                                    |  |  |  |

| 18       | 18       | SET1    | Set Monitored Threshold 1 Input. Monitor a voltage by setting the threshold with an external resistive divider. The SET1 threshold is 0.5V. It is recommended to have an input slew rate of 1V/15ms or faster.                                                                                                                                                                                                                                               |  |  |  |

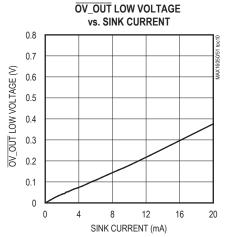

| 19       | 19       | OV_OUT  | Open-Drain Overvoltage Output. When any of the SET_ voltages exceed their 0.55V overvoltage threshold, $\overline{\text{OV\_OUT}}$ goes low. When all of the SET_ voltages are below their overvoltage threshold, $\overline{\text{OV\_OUT}}$ goes high impedance after a short propagation delay.                                                                                                                                                           |  |  |  |

| 20       | 20       | RESET   | Open-Drain Reset Output. When any of the monitored voltages (including EN) falls below its threshold, \$\overline{SHDN}\$ is pulled low, or \$\overline{FAULT}\$ is pulled low, \$\overline{RESET}\$ asserts and stays asserted for at least the minimum reset timeout period after all of these conditions are removed. The reset timeout is 128ms (typ) when TIMEOUT is connected to ABP or can be adjusted by connecting a capacitor from TIMEOUT to GND. |  |  |  |

| 21       | 21       | FAULT   | FAULT Synchronization Input/Output. While EN = SHDN = high, FAULT is pulled low when any of the SET_ voltages falls below their respective threshold. Pull FAULT low manually to assert a simultaneous power-down. FAULT is internally pulled up to ABP by a 100kΩ resistor.                                                                                                                                                                                 |  |  |  |

| 22       | 22       | SHDN    | Active-Low Shutdown Input. When $\overline{\text{SHDN}}$ is pulled low, the device will reverse sequence for power-down operation. $\overline{\text{SHDN}}$ is internally pulled up to ABP by a 100k $\Omega$ resistor.                                                                                                                                                                                                                                      |  |  |  |

| 23       | 23       | DELAY   | Adjustable Sequence Delay Timing Input. Connect a capacitor from DELAY to GND to set the sequence delay between each OUT Leave DELAY unconnected for a 10µs (typ) delay. The capacitor-adjusted delay occurs on power-up, not on power down.                                                                                                                                                                                                                 |  |  |  |

| 24       | 24       | TIMEOUT | Adjustable Reset Timeout Input. Connect a capacitor from TIMEOUT to GND to set the reset timeout period. Connect TIMEOUT to ABP for the fixed timeout of 128ms (typ). Leave TIMEOUT unconnected for a 10µs (typ) delay.                                                                                                                                                                                                                                      |  |  |  |

<sup>\*</sup>This applies to the MAX16051. For the MAX16050, see <u>Table 1</u> for the output sequence order.

## **Pin Description (continued)**

| PI       | N        | NAME   | FUNCTION                                                                                                                                                                                                          |

|----------|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16050 | MAX16051 | NAME   | FUNCTION                                                                                                                                                                                                          |

| 25       | _        | SEQ1   |                                                                                                                                                                                                                   |

| 26       | _        | SEQ2   | Sequence Order Select Inputs. SEQ1, SEQ2, and SEQ3 allow the order of sequencing for each supply to be programmable (Table 1).                                                                                    |

| 27       | _        | SEQ3   | cach cappy to be programmable (table 1).                                                                                                                                                                          |

| 28       | 28       | CP_OUT | Charge-Pump Output. An internal charge pump boosts CP_OUT to ( $V_{CC}$ + 5V ) to provide a pullup voltage that can be used to drive external n-channel MOSFETs. CP_OUT sources up to 25 $\mu$ A.                 |

| _        | 25       | DISC5  | Discharge Pulldown Input 5. During normal operation, DISC5 is high impedance. During a fault condition or power-down, DISC5 provides an 85mA sink current.                                                        |

| _        | 26       | OUT5   | Open-Drain Output 5. When the voltage at SET4 is above 0.5V, OUT5 goes high impedance. OUT5 requires an external pullup resistor and can be pulled up to $V_{CC}$ .                                               |

| _        | 27       | SET5   | External Set Monitored Threshold 5. Monitor a voltage by setting the threshold with an external resistive divider. The SET5 threshold is 0.5V. It is recommended to have an input slew rate of 1V/15ms or faster. |

| _        | _        | EP     | Exposed Pad. EP is internally connected to GND. Connect EP to the GND plane for improved heat dissipation. Do not use EP as the only ground connection.                                                           |

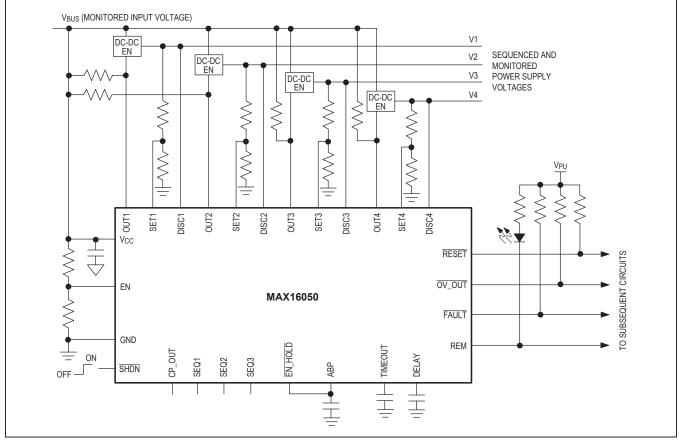

Figure 1. Typical Application Circuit for Sequencing Four DC-DC Converters

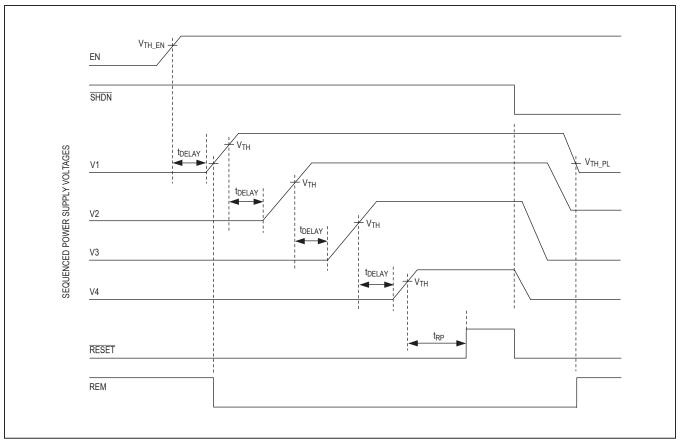

Figure 2. Sequencing Timing Diagram with Reverse Order Power-Down Using SHDN. See the Typical Application Circuit (Figure 1).

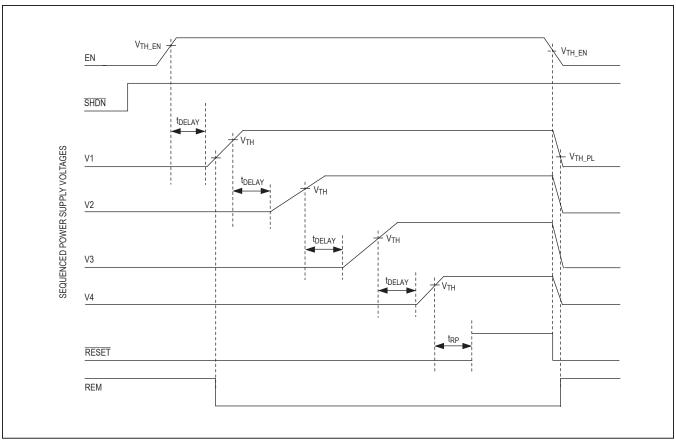

Figure 3. Sequencing Timing Diagram with Simultaneous Order Power-Down Using EN. See the Typical Application Circuit (Figure 1).

Figure 4. Sequencing Timing Diagram During a System Fault. See the Typical Application Circuit (Figure 1).

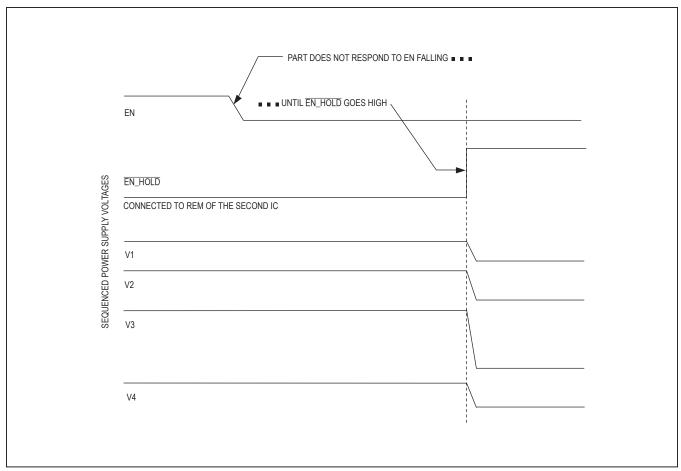

Figure 5. Power-Down Characteristics when REM of the Second IC is Connected to  $\overline{EN\_HOLD}$  of the First IC. See the Typical Application Circuit (Figure 1).

## **Functional Diagram**

## Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

#### **Detailed Description**

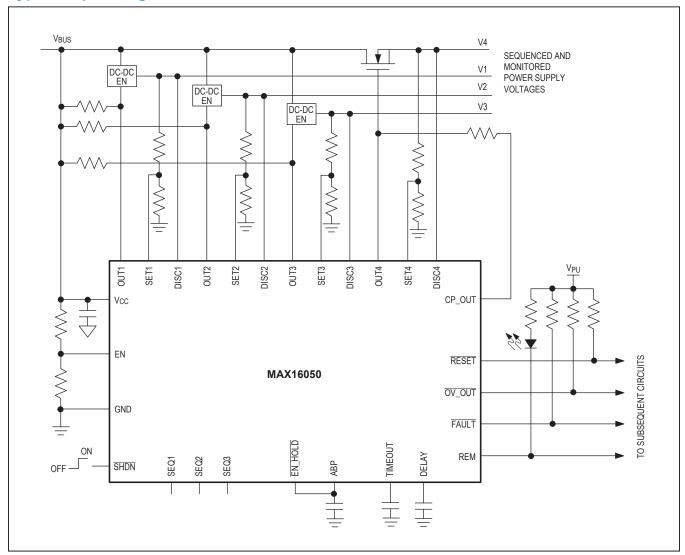

The MAX16050 monitors up to 5 voltages (Figure 1) with the ability to sequence up to 4 voltages, while the MAX16051 monitors up to 6 voltages with the ability to sequence up to 5 voltages. These devices control system power-up and power-down in a particular sequence order. The MAX16050/MAX16051 turn off all supplies and assert a reset to the processor when any of the voltages falls below its respective threshold. The MAX16050/MAX16051 offer an 85mA pulldown feature that helps discharge the output capacitance of DC-DC converters to ensure timely power-down. In addition, the MAX16050/MAX16051 also reverse sequence, monitoring each power-supply output voltage present at the associated DISC\_input and ensuring that the voltage falls below 250mV before turning off the next supply.

The MAX16050 provides three sequence logic inputs, which select the sequence order from 24 possible combinations (Table 1). In the default mode (SEQ1 = SEQ2 = SEQ3 = High Impedance), the power-up sequence is OUT1→OUT2→OUT3→OUT4. The MAX16051 features an additional channel and the sequence order is fixed at OUT1→OUT2→OUT3 →OUT4→OUT5. For complex systems with a large number of power supplies, the MAX16050/MAX16051 can be used in a daisy-chain configuration. Reverse sequencing in the daisy-chained configuration is still possible.

The MAX16050/MAX16051 keep all OUT\_ low (all of the supplies in the off-state) until four conditions are met.

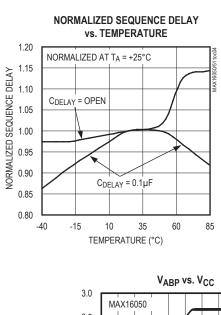

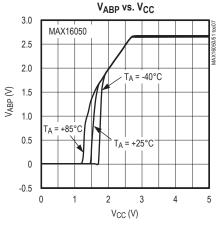

- The voltage at ABP exceeds the undervoltage lockout threshold. See V<sub>ABP</sub> vs. V<sub>CC</sub> curve in Typical Operating Characteristics.

- 2) The voltage at the analog enable input (EN) is above its threshold.

- 3) The shutdown input, SHDN, is not asserted.

- 4) All DISC voltages must be below 250mV.

When all of these conditions are met, independent of the order, the device starts the power-sequencing process by turning on OUT1-OUT in the sequence order. The sequence delay between each OUT is the time required for the power-supply voltage to exceed the undervoltage threshold plus the additional time delay set by the external delay capacitor; if no capacitor is connected to the sequence delay timing input (DELAY), only a short propagation delay (10µs) occurs. As each voltage meets its respective threshold, the next OUT\_ in the sequence goes high impedance (open-drain output), allowing the next power supply to turn on, which is then monitored by the next SET input. When all of the voltages exceed their respective thresholds, the reset output (RESET) deasserts after a reset timeout period to allow the system controller to start operating.

During sequenced turn-on, there is no time limit on any power supply output to come up. The device waits until a SET\_ input with a recommended ramp rate of at least 1V/15ms or faster goes above its threshold before asserting the corresponding OUT\_ pin high.

After sequencing is complete, if any SET\_ input drops below its threshold, a fault is detected, and all power supplies are simultaneously turned off by the OUT\_ outputs asserting low\_. Additionally, the RESET output asserts low, the DISC\_ current pulls down turn on, and the FAULT output pulls low for at least 1.9µs. The MAX16050/MAX16051 will then be ready to power on again. Sequencing begins as soon as the four startup conditions are met.

#### Sequencing

The MAX16050 features three three-state sequence logic inputs that select one of the 24 possible sequence orders (Table 1). These inputs allow the sequence order to be changed even after the board layout is finalized. The MAX16051 offers five channels and the device powers up in a fixed order from OUT1 to OUT5.

Table 1. MAX16050 Sequencing Table Logic

| SE04   | SEQ2   | SEQ3   |              | SEQUENC       | E ORDER     |               |

|--------|--------|--------|--------------|---------------|-------------|---------------|

| SEQ1   | SEQ2   | SEQS   | FIRST SUPPLY | SECOND SUPPLY | THIRD SUPPY | FOURTH SUPPLY |

| High-Z | High-Z | High-Z | OUT1         | OUT2          | OUT3        | OUT4          |

| High-Z | High-Z | Low    | OUT1         | OUT2          | OUT4        | OUT3          |

| High-Z | High-Z | High   | OUT1         | OUT3          | OUT2        | OUT4          |

| High-Z | Low    | High-Z | OUT1         | OUT3          | OUT4        | OUT2          |

| High-Z | Low    | Low    | OUT1         | OUT4          | OUT2        | OUT3          |

| High-Z | Low    | High   | OUT1         | OUT4          | OUT3        | OUT2          |

| High-Z | High   | High-Z | OUT2         | OUT1          | OUT3        | OUT4          |

| High-Z | High   | Low    | OUT2         | OUT1          | OUT4        | OUT3          |

| High-Z | High   | High   | OUT2         | OUT3          | OUT1        | OUT4          |

| Low    | High-Z | High-Z | OUT2         | OUT3          | OUT4        | OUT1          |

| Low    | High-Z | Low    | OUT2         | OUT4          | OUT1        | OUT3          |

| Low    | High-Z | High   | OUT2         | OUT4          | OUT3        | OUT1          |

| Low    | Low    | High-Z | OUT3         | OUT1          | OUT2        | OUT4          |

| Low    | Low    | Low    | OUT3         | OUT1          | OUT4        | OUT2          |

| Low    | Low    | High   | OUT3         | OUT2          | OUT1        | OUT4          |

| Low    | High   | High-Z | OUT3         | OUT2          | OUT4        | OUT1          |

| Low    | High   | Low    | OUT3         | OUT4          | OUT1        | OUT2          |

| Low    | High   | High   | OUT3         | OUT4          | OUT2        | OUT1          |

| High   | High-Z | High-Z | OUT4         | OUT1          | OUT2        | OUT3          |

| High   | High-Z | Low    | OUT4         | OUT1          | OUT3        | OUT2          |

| High   | High-Z | High   | OUT4         | OUT2          | OUT1        | OUT3          |

| High   | Low    | High-Z | OUT4         | OUT2          | OUT3        | OUT1          |

| High   | Low    | Low    | OUT4         | OUT3          | OUT1        | OUT2          |

| High   | Low    | High   | OUT4         | OUT3          | OUT2        | OUT1          |

## Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

#### Reset Voltage V<sub>CCR</sub>

The MAX16050/MAX16051 monitor  $V_{CC}$  to ensure the DISC\_, OUT\_, and  $\overline{RESET}$  pins are at the right level when  $V_{ABP}$  goes below  $V_{UVLO}$ .  $V_{CCR}$  is the lowest value of  $V_{CC}$  for which these three pin types are guaranteed to be low. When a falling  $V_{CC}$  goes below 2.2V typical, the regulated supply voltage  $V_{ABP}$  falls below  $V_{UVLO}$ . See  $V_{ABP}$  vs.  $V_{CC}$  curve in the Typical Operating Characteristics. When  $V_{ABP}$  is below  $V_{UVLO}$ , and  $V_{CC}$  is higher than  $V_{CCR}$ , DISC\_, OUT\_, and  $\overline{RESET}$  are all asserted low. For  $V_{CC}$  below  $V_{CCR}$ , these pin voltages are indeterminate. The  $\overline{FAULT}$  output behaves differently. Its voltage becomes indeterminate as soon as  $V_{ABP}$  falls below  $V_{UVLO}$ .

#### **Charge-Pump Output (CP\_OUT)**

The MAX16050/MAX16051 feature an on-chip charge pump that drives its output voltage to 5V above  $V_{CC}$ , and it can be used as a pullup voltage to drive one or more external n-channel MOSFETs (see the *Typical Operating Circuit*). The charge-pump output can be modeled as a 25µA current source with a compliance voltage of ( $V_{CC}$  + 5V); the slew rate can be controlled by connecting a capacitor from the gate of the MOSFET to ground. When using CP\_OUT to provide the pullup voltage for multiple MOSFETs, ensure that the voltage is enough to enhance a MOSFET despite the load of the other pullup resistors (which may be connected to outputs that are deasserted low).

#### **Disabling Channels**

If any channel is not used, connect the associated SET\_input to ABP. Connect DISC\_ of the disabled channel to GND. Do not leave the SET\_ or DISC\_ inputs disconnected. Disabling any one channel does not disable the other channels. This channel exclusion feature adds more flexibility to the device in a variety of different applications.

#### **SHDN** and EN Inputs

The shutdown input (SHDN) initiates a reverse sequencing event. When SHDN is brought low, the device will sequentially power down in reverse order. During this period, all DISC\_ inputs are monitored to make sure the voltage of each supply falls below 250mV before allowing the next supply to shut down. The next OUT\_ goes low as soon as the previous DISC\_ input drops below 250mV without any capacitor-adjusted delay. This continues until all supplies are turned off. SHDN is internally pulled up to ABP.

When EN falls below its threshold, the device performs a simultaneous power-down and does not reverse sequence. When either  $\overline{\text{SHDN}}$  or  $\overline{\text{EN}}$  initializes the power-down event, the reset output ( $\overline{\text{RESET}}$ ) immediately asserts. At the end of the power-down event, when all DISC\_ voltages are below 250mV, the bus removal output (REM) goes high impedance.  $\overline{\text{SHDN}}$  and EN must be low for a minimum pulse width before the device responds. See the *Electrical Characteristics* Table.

For applications where both EN and SHDN go low, the MAX16050/MAX16051 will ignore EN if it is taken low any time after SHDN is asserted. However, for a simultaneous power-down using the EN pin, SHDN must not be asserted within the EN to OUT\_ Delay after EN is taken low. Otherwise, it can initiate a reverse-sequence shutdown. See the *Electrical Characteristics* Table.

#### Reset Output (RESET)

The MAX16050/MAX16051 include a reset output. RESET is an open-drain output and requires an external pullup resistor.

When any of the monitored voltages falls below its threshold, SHDN is pulled low, EN falls below its threshold, or FAULT is pulled low, RESET asserts and stays asserted for at least the minimum reset timeout period after all of these conditions are removed. Connect a capacitor from TIMEOUT to GND to adjust the reset timeout period. Connect TIMEOUT to ABP for the fixed timeout of 128ms (typ). Leave TIMEOUT unconnected for a 10µs (typ) timeout period.

#### **FAULT** Input/Output

The  $\overline{FAULT}$  input/output asserts to signal a fault if any of the SET\_ monitored voltages falls below its threshold while EN =  $\overline{SHDN}$  = high.  $\overline{FAULT}$  is internally pulled up to ABP by a 100k $\Omega$  resistor.  $\overline{FAULT}$  also can be used as an input. Pull  $\overline{FAULT}$  low to simultaneously shut down the OUT\_ outputs.

For multichip solutions, all of the FAULT input/outputs can be connected together. In case of a fault condition, all outputs on every device are turned off and the internal pull-down circuitry is activated simultaneously. FAULT must be low for at least trault pw before the device responds.

## Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

#### Overvoltage Fault Output (OV\_OUT)

The MAX16050/MAX16051 include an overvoltage fault output.  $\overline{\text{OV}_{-}\text{OUT}}$  is an open-drain output and requires an external pullup resistor. When any of the SET\_ voltages exceed their 0.55V overvoltage threshold,  $\overline{\text{OV}_{-}\text{OUT}}$  goes low. When all of the SET\_ voltages are below their overvoltage threshold,  $\overline{\text{OV}_{-}\text{OUT}}$  goes high impedance after a short propagation delay. To force OUT\_ low during an overvoltage condition,  $\overline{\text{OV}_{-}\text{OUT}}$  must be externally connected to  $\overline{\text{FAULT}}$ .

#### Discharge Inputs (DISC\_)

The DISC\_ inputs connect to sequenced power supply outputs, and discharge power-supply capacitors during a power-down or fault event. They monitor power-supply output voltages during reverse sequencing. When an OUT\_ pin goes low, the associated DISC\_ activates an 85mA pulldown current to discharge any output capacitors. This helps the power-supply output drop below the 250mV level so the next power supply can be turned off. During normal operation, DISC\_ is high impedance and will not load the circuit.

#### **Bus Removal Output (REM)**

The MAX16050/MAX16051 include an open-drain bus removal output (REM) that indicates when it is safe to disconnect the input power after a controlled power-down operation. REM monitors DISC\_ voltages and goes low when any DISC\_ input voltage goes above the DISC\_ power low threshold (V<sub>TH\_PL</sub>). REM goes high when all DISC\_ inputs are below the DISC\_ power low threshold (V<sub>TH\_PL</sub>). For a visual signal of when it is unsafe to remove a powered board from the bus, connect an LED to REM.

#### **Enable Hold Input (EN HOLD)**

When EN\_HOLD is low, a high-to-low transition on SHDN or on EN is ignored. EN\_HOLD must be high for SHDN or EN to disable the device. This feature is used when multiple MAX16050/MAX16051s are daisy-chained (see Figure 7). Connect EN\_HOLD to ABP if not used.

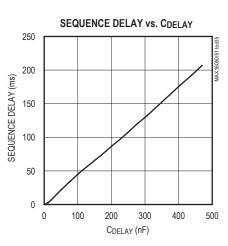

#### **Delay Time Input (DELAY)**

Connect a capacitor ( $C_{DELAY}$ ) between DELAY and GND to adjust the sequencing delay period ( $t_{DELAY}$ ) that occurs between sequenced channels. Use the following formula to estimate the delay:

$$t_{DELAY} = 10\mu s + (500k\Omega \times C_{DELAY})$$

where  $t_{\mbox{\scriptsize DELAY}}$  is in seconds and  $C_{\mbox{\scriptsize DELAY}}$  is in Farads. Leave DELAY unconnected for the default 10µs (typ) delay.

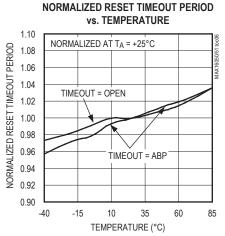

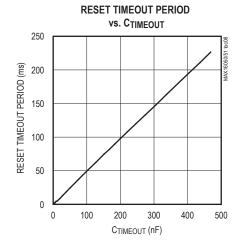

#### **Reset Timeout Input (TIMEOUT)**

Connect a capacitor ( $C_{TIMEOUT}$ ) from TIMEOUT to GND to set the reset timeout period. After all SET\_ inputs exceed their thresholds ( $V_{TH}$ ),  $\overline{RESET}$  remains low for the programmed timeout period,  $t_{RP}$ , before deasserting (see Figure 2). Use the following formula to estimate the reset timeout period:

$$t_{RP} = 10\mu s + (500k\Omega \times C_{TIMEOUT})$$

where  $t_{RP}$  is in seconds and  $C_{TIMEOUT}$  is in Farads. Leave TIMEOUT unconnected for the default 10 $\mu$ s (typ) timeout delay or connect TIMEOUT to ABP to enable a fixed 128ms (typ) timeout.

#### **Applications Information**

#### **Resistor Value Selection**

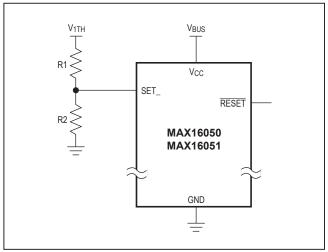

The MAX16050/MAX16051 feature four and five SET\_inputs, respectively, and the threshold voltage ( $V_{TH}$ ) at each SET\_input is 0.5V (typ). To monitor a voltage  $V_{1TH}$ , connect a resistive divider network to the circuit as shown in Figure 6, and use the following equation to calculate the monitored threshold voltage:

$$V_{1TH} = V_{TH} \times \left(1 + \frac{R1}{R2}\right)$$

Balance accuracy and power dissipation when choosing the external resistors. The input to the voltage monitor is a high-impedance input with a small 100nA leakage current. This leakage current contributes to the overall error of the threshold voltage, and this error is proportional to the value of the resistors used to set the threshold. Small-valued resistors reduce the error but increase the power

Figure 6. Setting the SET\_ Input

## Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

consumption. Use the following equation to estimate the value of the resistors based on the amount of acceptable error:

$$R1 = \frac{e_A \times V_{1TH}}{I_{SFT}}$$

where  $e_A$  is the fraction of the maximum acceptable absolute resistive divider error attributable to the input leakage current (use 0.01 for  $\pm 1\%$ ),  $V_{1TH}$  is the powergood threshold for the power supply being monitored, and  $I_{SET}$  is the worst-case  $SET_$  input leakage current (see the *Electrical Characteristics* table). Calculate R2 as follows:

$$R2 = \frac{V_{TH} \times R_1}{V_{1TH} - V_{TH}}$$

The eA error adds to any errors caused by the resistive voltage divider.

#### **Pullup Resistor Values**

The exact value of the pullup resistors for the open-drain outputs is not critical, but some consideration should be made to ensure the proper logic levels when the device is sinking current. For example, if  $V_{CC}$  = 3.3V and the pullup voltage is 5V, keep the sink current less than 3.2mA as shown in the *Electrical Characteristics* table. As a result, the pullup resistor should be greater than 1.6k $\Omega$ . For a 12V pullup, the resistor should be larger than 3.74k $\Omega$ .

Extra care must be taken when using CP\_OUT as the pullup voltage. If multiple pullup resistors are connected to CP\_OUT, any OUT\_ pin that goes low will draw a current from CP\_OUT. If this current is too high, it can drop the CP\_OUT voltage enough to prevent other enabled MOSFETs from turning on completely. See CP\_OUT VOLTAGE vs. CP\_OUT CURRENT in the *Typical Operating Characteristics*.

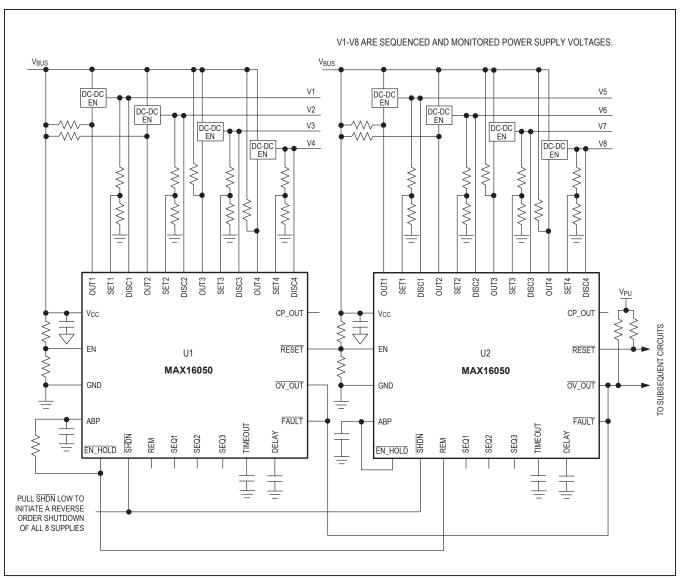

#### Daisy-Chaining the MAX16050/MAX16051

Multiple MAX16050/MAX16051 devices can be daisy-chained to sequence and monitor a large number of voltages Figure 7 shows an example of two daisy-chained devices. When a fault occurs on any of the monitored inputs, FAULT goes low, signaling a fast power-down. Connect all FAULT pins of the MAX16050/MAX16051 together to ensure that all power supplies are turned off during a fault.

In Figure 7, for proper turn-on, U1 RESET is connected to U2 EN to ensure power-up sequencing for all voltage rails. For turn off, SHDN is pulled low to initiate the power-down sequence. When all of the supply voltages monitored by U2 are off, the bus removal output (REM) goes high, thereby allowing U1 to start sequencing down. REM normally is at a logic-low state when all voltages are good. Connect U2's REM to U1's EN\_HOLD to force U1 to stay on even if EN and SHDN are pulled low. This enable-and-hold circuitry allows the system to power down correctly.

#### **MOSFET Selection**

The external pass MOSFET connects in series with the sequenced power-supply source. Since the load current and the MOSFET drain-to-source impedance (R<sub>DSON</sub>) determine the voltage drop, the on-characteristics of the MOSFET affect the load supply accuracy. For highest supply accuracy and lowest voltage drop, select a MOSFET with an appropriate drain-to-source on-resistance with a gate-to-source bias of 4.5V to 6.0V (see Table 2).

#### Layout and Bypassing

For better noise immunity, bypass  $V_{CC}$  to GND with a 0.1 $\mu$ F capacitor installed as close to the device as possible. Bypass ABP to GND with a 1 $\mu$ F capacitor installed as close to the device as possible. Connect the exposed pad (EP) to the ground plane for improved heat dissipation. Do not use EP as the only ground connection for the device.

# Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

**Table 2. Recommended MOSFETs**

| MANUFACTURER               | PART                 | V <sub>DS</sub><br>(V) | V <sub>GSth</sub> (V) | $R_{DSON}$ AT $V_{GS} = 4.5V$ (m $\Omega$ ) | I <sub>MAX</sub> AT 50mV<br>VOLTAGE DROP (A) | Qg (nC)<br>(TYP) | FOOTPRINT                               |

|----------------------------|----------------------|------------------------|-----------------------|---------------------------------------------|----------------------------------------------|------------------|-----------------------------------------|

|                            | FDC633N              | 30                     | 0.67                  | 42                                          | 1.19                                         | 11               | Super<br>SOT-6                          |

| Fairchild                  | FDP8030L<br>FDB8030L | 30                     | 1.5                   | 4.5                                         | 11.11                                        | 120              | TO-220<br>TO-263AB                      |

|                            | FDD6672A             | 30                     | 1.2                   | 9.5                                         | 5.26                                         | 33               | TO-252                                  |

|                            | FDS8876              | 30                     | 2.5<br>(max)          | 17                                          | 2.94                                         | 15               | SO-8                                    |

|                            | Si7136DP             | 20                     | 3                     | 4.5                                         | 11.11                                        | 24.5             | SO-8                                    |

|                            | Si4872DY             | 30                     | 1                     | 10                                          | 5                                            | 27               | SO-8                                    |

| Vishay                     | SUD50N02-09P         | 20                     | 3                     | 17                                          | 2.94                                         | 10.5             | TO-252                                  |

|                            | Si1488DH             | 20                     | 0.95                  | 49                                          | 1.02                                         | 6                | SOT-363<br>SC70-6                       |

|                            | IRL3716              | 20                     | 3                     | 4.8                                         | 10.4                                         | 53               | TO220AB<br>D <sup>2</sup> PAK<br>TO-262 |

| International              | IRL3402              | 20                     | 0.7                   | 10                                          | 5                                            | 78 (max)         | TO-220AB                                |

| International<br>Rectifier | IRL3715Z             | 20                     | 2.1                   | 15.5                                        | 3.22                                         | 7                | TO220AB<br>D <sup>2</sup> PAK<br>TO-262 |

|                            | IRLML2502            | 20                     | 1.2                   | 45                                          | 1.11                                         | 8                | SOT23-3<br>Micro3                       |

Figure 7. Daisy-Chaining Two Devices to Sequence Up to 8 Voltages

## **Typical Operating Circuit**

Figure 8. Example Circuit Showing 3 Power Supplies, and a MOSFET Turned On and Off in Sequence (CP\_OUT is used to provide the MOSFET gate drive)

# Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE | MONITORED VOLTAGES | VOLTAGES<br>SEQUENCED |

|--------------|----------------|-------------|--------------------|-----------------------|

| MAX16050ETI+ | -40°C to +85°C | 28 TQFN-EP* | 5                  | 4                     |

| MAX16051ETI+ | -40°C to +85°C | 28 TQFN-EP* | 6                  | 5                     |

<sup>+</sup>Denotes lead-free/RoHS-compliant package.

### **Chip Information**

PROCESS: BiCMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.analog.com/packages">www.analog.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 28 TQFN | T2844-1 | 21-0139 | 90-0035     |

<sup>\*</sup>EP = Exposed paddle.

## Voltage Monitors/Sequencer Circuits with Reverse-Sequencing Capability

## **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                 | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 11/07            | Initial release                                                                                                                                             | _                |

| 1                  | 7/08             | Revised Electrical Characteristics and Disabling Channels sections.                                                                                         | 2, 3, 15         |

| 2                  | 5/17             | Max V <sub>CC</sub> increased to 16V, addressing multiple customer questions, fixing several errors and ambiguities, updating data sheet format and layout. | 1–24             |

| 3                  | 3/24             | Updated Pin Description and Detailed Description                                                                                                            | 7–9, 15          |